— полевой транзистор с изолированным затвором.

Оглавление

Введение………………………………………………………......5

1. Элементы памяти для биполярных СБИС ОЗУ…………5

2. Элементная база схем управления СБИС ОЗУ……..…..8

3. Варианты организации режима работы схем управления СБИС ОЗУ.......................................11

4. Заключение…………………..…………………………….....12

5. Литература…………….………………………………………14

Введение

Требования, предъявляемые к быстродействию и объему памяти полупроводниковых ЗУ, непрерывно возрастают. Для реализации этих требований разрабатываются и производятся сверхбольшие: интегральные схемы (СБИС) ОЗУ на биполярных и МДП-транзисторах, которые достигли к настоящему времени информационной емкости 4 и 16 кбит. Основные причины, сдерживающие рост информационного объема СБИС ОЗУ — жесткие ограничения на мощность, рассеиваемую микросхемой Р<0,5 Вт/корпус (без специального, охлаждения), и площадь кристалла: S_(озу ) 20÷30 〖мм〗^2. Существенное преимущество биполярных элементов памяти по быстродействию позволяет сделать вывод о перспективно*!* этой элементной базы для СБИС ОЗУ. Поэтому представляет интерес анализ возможности достижения предельной емкости памяти на их основе и оценка технических характеристик таких ОЗУ.

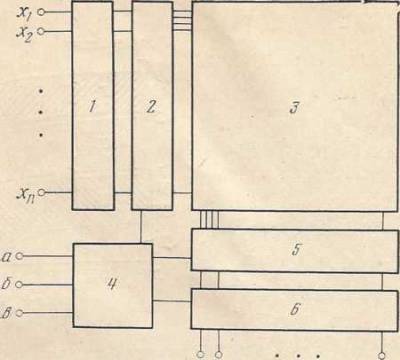

Типовая структурная блок-схема СБИС ОЗУ содержит матрицу микромощных элементов памяти (ЭП) или накопитель, занимающий 60—80% площади кристалла, и схемы управления (СУ), включающие в себя адресные формирователи и разрядные формирователи-предусилители дешифраторы адреса и схему выборки кристалла.

Элементы памяти для биполярных СБИС ОЗУ

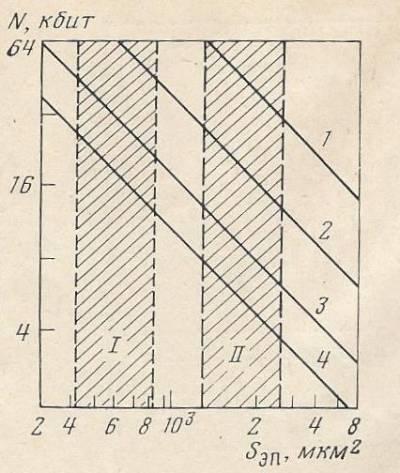

Выбор ЭП для СБИС ОЗУ в первую очередь связан с удовлетворением ограничения на допустимую площадь кристалла. Так как обычно ЭП занимает центральную часть кристалла, а СУ размещаются по периметру в полосе шириной 1,0÷1,5 мм, можно определить допустимую площадь ЭП (S_эп) в зависимости от требуемой емкости микросхемы памяти (N). Площадь кристалла при этом является параметром (рис. 2); для реализации СБИС ОЗУ емкостью, например, 16 кбит на кристалле с S_озу=20-30 〖мм〗^2 необходимо применять ЭП с S_эп=1000 〖мкм〗^2.

Рис. 1. Типовая структура микросхемы памяти:

1 — дешифратор х;

2 -адресные формирователи;

3 - матрица ЭП;

4 - схема выборки кристалла, а - вход информации, б - выход информации, выборка кристалла;

5 - разрядные формирователи-предусилители;

В биполярных СБИС ОЗУ могут использоваться статические и динамические ЭП, причем наименьшую площадь имеют ЭП с инжекционным питанием. В частности, статические инжекционные ЭП имеют минимальную» S_эп=1500÷2500 〖мкм〗^2 и рассеивают в режиме хранения мощность P_(хр.эп)=10 ...1 мкВт и менее. При организации двухуровневого режима работы, когда при записи и считывании через выбранный ЭП протекает: больший ток, чем в режиме хранения информации, эти ЭП имеют достаточно высокое быстродействие 〖 t〗_зп,t_сч=20÷80 нс. В качестве недостатка рассматриваемых ЭП можно указать необходимость межразрядной изоляции в накопителе.

Рис. 2 Предельный объем памяти СБИС ОЗУ в зависимости от площади (S_эп) и типа используемого ЭП и площади кристалла (S_озу).

I — динамические ЭП с инжекционным питанием;

II — статические инжекционные ЭП; S_озу, 〖мм〗^2:

1=100; 2 — 50; 3 — 30; 4 — 20

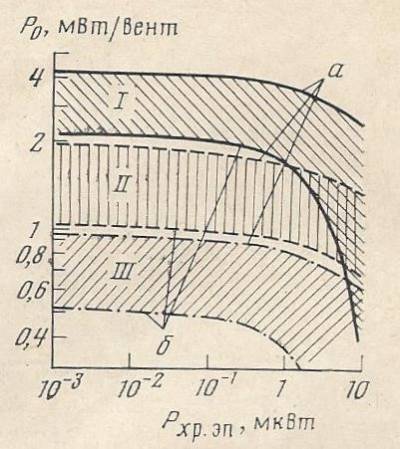

Рис. 3. Предельная мощность вентиля СУ (P_0) СБИС ОЗУ в зависимости от емкости (N), мощности рассеиваемой корпусом микросхемы (P_озу ) и мощности хранения ЭП

(P_(хр.эп)), N, кбит: 1 — 4;

II - 16;

III - 65; а - P_озу=1000 мВт, б - 500

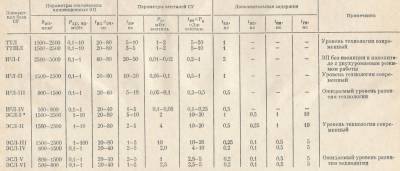

В табл. 1 приведены параметры статических инжекционных ЭП. Некоторые варианты ЭП с площадью S_эп≤1500 〖мкм〗^(2 )и P_(хр.эп)=0,1÷1,0 мкВт могут быть реализованы с помощью новых вариантов технологии схем с инжекционным питанием. В частности, в качестве таких вариантов можно назвать технологию с вертикальной инжекцией (〖ВИ〗^2 Л) [7], изопланарной инжекционной логики (И^3 Л) [8], технологию с самосовмещенными двойными Инжекторами (〖ДИ〗^2 Л) [9]. Отметим, что для оценки СБИС ОЗУ с накопителем, не требующим межразрядной изоляции и СУ, на основе И^2 Л - схем использован ЭП, имеющий достаточно малую площадь S_эп=2500÷5000 〖мкм〗^2 по сравнению с ЭП, предложенным в [5]. Данные предположения отражают ожидаемый уровень развития технологии биполярных ИС.

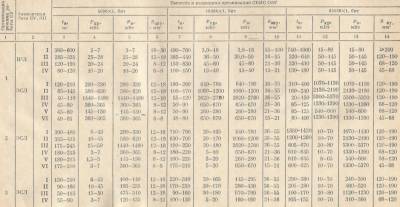

Табл. 1. Параметры статических инжекционных ЭП и различных вариантов вентилей СУ

Элементная база схем управления СБИС ОЗУ

Выбор элементной базы для СУ биполярных микросхем памяти определяется допустимой потребляемой мощностью и требуемым высоким быстродействием. Схемы управления могут работать в статическом и динамическом режиме питания. Статические СУ обеспечивают высокое быстродействие, но потребляют значительную мощность.

Определим ограничения на мощность, потребляемую вентилями статических СУ (P_0) для СБИС ОЗУ. На рис. 3 представлены зависимости P_0 от мощности, потребляемой ЭП, емкости микросхемы и допустимой мощности, рассеиваемой корпусом (P_озу). Видно, что для. СБИС ОЗУ емкость, например, 16 кбит и P_озу=500 мВт необходимо использовать, вентили с P_0≤1 мВт. В статических СУ возможно применение вентилей на базе маломощных ТТЛ-схем, элементов ТТЛШ, ЭСЛ и 〖 И〗^2 Л. Однако ТТЛ, ТТШЛ и ЭСЛ-схемы значительно уступают И^2 Л - схемам по параметру потребляемой мощности (табл.1), требуют специальных корпусов для СБИС ОЗУ или принудительного охлаждения (рис. 3). Поэтому для статических СУ наиболее перспективной является элементная база И^2 Л (табл. 1): И^2 Л— I, изготовленные по стандартной технологии без изоляции компонентов;〖 И〗^2 Л — II, изготовленные по технологии с окисной изоляцией; И^2 Л — III с неиспользованием перспективных вариантов технологии И^2 Л-схем, например: И^3 Л, 〖ДИ〗^2 Л, 〖ВИ〗^2 Л и др.; И^3 Л — IV в расчете на ожидаемый уровень развития технологии И^2 Л-схем.

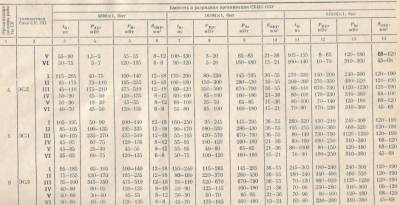

Табл. 2. Технические характеристики СБИС ОЗУ на

биполярных транзисторах емкостью 4-65 кбит.

Основная трудность использования инжекционных СУ заключается в необходимости построения мощных импульсных источников тока, возможность реализации которых практически еще не исследована: Импульсные источники необходимы для организации двухуровневого режима работы ЭП, формирования управляющих и выходных сигналов.

Динамический режим работы СУ характеризуется тем, что они подключаются к источнику питания только в режиме обращения к СБИС ОЗУ, причем лишь та необходимая часть вентилей, которая определяется кодом адреса выбираемого ЭП. Такой режим работы СУ позволяет существенно сократить потребляемую мощность, но может вызвать некоторое снижение быстродействия за счет задержки подключения СУ источнику питания. Избежать снижения быстродействия можно с помощью увеличения потребляемой мощности (и быстродействия) вентилей; которые наиболее существенно влияют на быстродействие СБИС ОЗУ, поскольку в данном случае ограничения на P_(0 )менее существенны, чем для статических СУ (рис. 3). Кроме того, часть вентилей СУ можно вообще сделать статическими или производить их предварительное подключение к источнику питания по сигналу выборки кристалла. Далее будут рассмотрены некоторые варианты статико-динамического режима работы СБИС ОЗУ.

Для динамических СУ могут быть выбраны различные типы логических схем с И^2 Л, ТТЛ-схемы и т. д. Целесообразно применять импульсные переключатели тока на основе ЭСЛ-схем, имеющих высокое быстродействие [10]. В табл. 1 приведено несколько вариантов ЭСЛ-схем для динамических СУ. Следует отметить, что вентили (ЭСЛ —- I) ЭСЛ — II, ЭСЛ — III с фактором качества (P_(0 )х t_30) =10÷20 пДж характеризуют современный уровень развития технологии биполярных приборов, а - ЭСЛ — IV, ЭСЛ — У, ЭСЛ — VI с (P_0 x t_30) =5÷12 пДж — ожидаемый. Недостатком применения импульсных переключателей тока на основе - ЭСЛ-схем является трудность реализации в едином технологическом процессе микромощных инжекционных ЭП и быстродействующих ЭСЛ-схем управления.

Варианты организации режима работы схем управления СБИС ОЗУ

Возможна различная организация режима работы СУ [14]:

1) все СУ статические;

2) питание всех СУ импульсное, обеспечивается схемой выборки кристалла;

3)схемы групповой выборки введены в структурную блок-схема СБИС ОЗУ (рис. 1);

4) схемы групповой выборки и схема выборки кристалла — статические, остальные СУ — импульсные;

5) схемы групповой выборки, связанные с ними входные буферные «схемы и схема выборки кристалла — статические, остальные СУ — импульсные;

6) схемы декодирования и формирователи — импульсные, остальные СУ — статические.

Для каждого из указанных вариантов режима работы СУ при различных сочетаниях параметров вентилей и микромощных инжекционных: ЭП проведены оценки основных параметров СБИС ОЗУ емкость 4÷65 кбит. Результаты расчета сведены в табл. 2, где S_озу — площадь кристалла, t_в — время цикла выборки информации, P_(хр ), P_в — мощности потребляемые в режиме хранения и выборки соответственно. Расчет проводился по методике, предложенной в работе [11].

При оценке параметров СБИС ОЗУ был выбран инжекционный ЭП с межразрядной изоляцией [4], кроме микросхем с СУ на основе И^2 Л — I вентилей, где применен ЭП, не требующий изоляции в накопителе (табл. 1). Задержка прохождения сигнала через накопитель при организации двухуровневого режима ЭП принята равной t_зп, t_сч=20÷80 нс.

Для статических СУ (варианты I ЭСЛ — I, I ЭСЛ — II, И^2 Л — I и т. д., табл. 2) предполагалось, что все вентили схем управления рассеивают практически одинаковую мощность.

При оценке быстродействия (t_в) считалось, что задержки прохождения сигнала через вентили СУ равны (за исключением схем групповой выборки с задержкой — t_(г*в)) и зависят от нагрузки: t_з= t_30+n×t_зд, где t_30 — задержка при коэффициенте разветвления по выходу n=1,t_зд,— дополнительная задержка при увеличении n числа нагрузок. Вентиль СУ | может оказывать на нагрузку пассивное воздействие, если нагрузочный вентиль не подключен к источнику питания (t_зд=t_зп) или логическое (t_зд=t_зл) в противоположном случае. Когда вентиль СУ служит в качестве импульсного питания, t_зд=t_зи (табл. 1).

В рассматриваемых СБИС ОЗУ предполагалось, что буферные схемы совмещены с первой ступенью дешифраторов, а формирователи — с последней (рис. 1).

Табл. 3. Сравнительная характеристика СБИС ОЗУ на биполярных и МДП-транзисторах

Заключение

Анализ возможностей реализации биполярных СБИС ОЗУ емкость» более 4 кбит показывает, что могут быть разработаны микросхемы памяти с высокими техническими характеристиками емкостью 4÷6 кбит на основе микромощных инжекционных ЭП и СУ на базе ЭСЛ — импульсным переключателей тока со статико-динамической организацией режима ран боты (табл. 3). При этом может быть обеспечено высокое быстродействие (t_в=50÷150 нс) и достаточно малое потребление мощности в режим хранения P_хр=20÷300 мВт. В зависимости от организации режима работы СУ потребление мощности в режиме выборки изменяется в значительных пределах и составляет P_в=20÷2000 мВт. Наилучшее сочетание технических характеристик СБИС ОЗУ достигается при введении в структурную блок-схему статических схем групповой выборки (табл. 2, варианты организации 3—6).

Полностью инжекционные статические СБИС ОЗУ на базе И^2 Л-схем более технологичны, так как не требуют изоляции компонентов. Однако подобные микросхемы памяти на современном уровне развития технологии и схемотехники будут значительно уступать по быстродействию статико-динамическим СБИС ОЗУ (t_в=200÷700 нс) при малой потребляемой мощности P_хр, P_в=3÷30 мВт (табл. 3). Реализация инжекционных микросхем памяти может быть рекомендована для недорогих БИС ОЗУ емкостью до 4 кбит со средним быстродействием (t_в=200÷300 нс). Для практической реализации инжекционных СБИС ОЗУ емкостью более 4 кбит требуются дальнейшие схемотехнические и технологические разработки. В частности, разработка высококачественных И^2 Л-вентилей с t_30=1÷5 нс и (P_0 х t_30)=1 пДж, инжекционных ЭП, не требующих межразрядной изоляции в накопителе, с небольшой площадью s_эп≤2500 〖мкм〗^2 импульсных источников тока на базе И^2 Л-схем. В этом случае могут быть реализованы СБИС ОЗУ с высоким быстродействием.

Таким образом, на достигнутом уровне биполярной технологии и схемотехники максимальный объём памяти ограничивается емкостью 16 кбит. Перспективы реализации биполярных схем памяти емкостью 32,65 кбит и более связаны с использованием динамических схем управления и динамических инжекционных запоминающих элементов.

ЛИТЕРАТУРА

1. Лапшинский В. А. Полупроводниковые биполярные СБИС памяти // Микроэлектроника.

— 1979.- №8. С. 302-311. 2. Лашинский В. А., Алексеенко А. Г. Суперкомпоненты на основе СБИС памяти // Микроэлектроника. — 1980.- №9. С.302-311.

3. Алексеенко А. Г., Онищенко Е. М. Микроэлектроника / Под ред. Алексеенко А. Г., 1975. №2. - С. 107.