| Статистика |

Онлайн всего: 1 Гостей: 1 Пользователей: 0 |

|

"Обзор СБИС памяти (1979)"

Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

Национальный исследовательский ядерный университет «МИФИ»

Факультет «Автоматики и электроники»

Кафедра «Микро- и наноэлектроника»

Домашнее задание №1

по дисциплине «Применение ПК»

на тему

«Обзор СБИС памяти (1979)»

Авторы статьи:

Д. т. н. Алексенко А.Г.

Лапшинский В.А.

Конспект выполнила:

студент группы А4-09

Я.А. Мисюченко

Преподаватель:

доцент В.А. Лапшинский

Москва 2013

Содержание

Обозначения и сокращения.......................................................................................................3

Введение..................................................................................................................................4

1 ТРАДИЦИОННАЯ СТРУКТУРА СБИС И ОСОБЕННОСТИ НЕКОТОРЫХ ТИПОВ СБИС ПАМЯТИ.....5

2 ПРИНЦИПЫ ПРОЕКТИРОВАНИЯ СБИС ПАМЯТИ.....................................................................6

2.1 Активно-пассивная организация питания СБИС памяти.......................................................6

2.2 Принцип «базового кристалла» с перестраиваемой организацией.......................................7

2.3 Принцип структурно-топологической избыточности.............................................................7

2.4 Многофункциональное использование связей матрицы с блоками управления.....................9

2.5 Способы неавтономной и автономной организации хранения...............................................9

3 СПОСОБЫ ВЫБОРКИ ИНФОРМАЦИЯ И ОРГАНИЗАЦИЯ СБИС ПАМЯТИ...................................11

3.1 Адресный поиск................................................................................................................11

3.2 Безадресный поиск...........................................................................................................12

3.3 Комбинированный адресно-ассоциативный поиск...............................................................12

3.4 Последовательный и параллельный ввод – вывод.............................................................13

4 ПЕРСПЕКТИВЫ РАЗВИТИЯ СБИС ПАМЯТИ И ЗУ НА ИХ ОСНОВЕ.............................................15

4.1 Проектирование ЗУ на основе СБИС памяти с «традиционной» организаций и многофункциональных интерфейсных БИС..........................................................................................................................................15

4.2 Проектирование цифровых систем на основе однородных вычислительных сред.................16

4.3 Новые подходы к структурной организации СБИС памяти и ЗУ на их основе........................16

ЗАКЛЮЧЕНИЕ.............................................................................................................................18

Список литературы....................................................................................................................19

Глоссарий

ИС – система интеллектуальная

ОЗУ – устройство оперативное запоминающее

ППЗУ – устройство программируемое постоянное запоминающее

ПЗУ – устройство постоянное запоминающее

ВЗУ – устройство внешнее запоминающее

АШ – шины адресные

РШ – шины разрядные

ШУ – шины управления

МОП-структура (металл — оксид — полупроводник) — наиболее широко используемый тип полевых транзисторов

Введение

Данная работа представляет собой выполнение ДЗ №1, которое связано со знанием Word. Здесь представлено умение пользоваться этим текстовым процессором, оформление конспекта в соответствии с ГОСТ-32.

В работе рассматривается состояние, особенности проектирования и перспективы развития сверхбольших интеллектуальных систем памяти на момент 1979 г. В то время наиболее перспективной элементной базой цифровых систем IV поколения являлись полупроводниковые сверхбольшие ИС (СБИС) микропроцессоров и памяти различных типов, степень интеграции которых достигла 1000-100000 компонентов и продолжает возрастать быстрыми темпами. В 1979 году возникла проблема разработки структурной организации и выбора перспективных принципов проектирования СБИС памяти большой информационной ёмкости.

1 ТРАДИЦИОННАЯ СТРУКТУРА СБИС И ОСОБЕННОСТИ НЕКОТОРЫХ ТИПОВ СБИС ПАМЯТИ

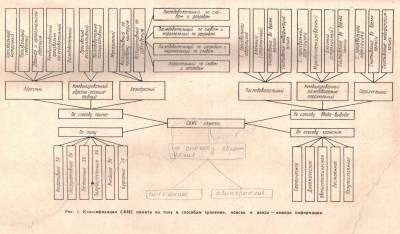

Основными типами СБИС памяти, которые в то время выпускались в интегральном виде, являлись следующие СБИС памяти: ОЗУ, АЗУ, БЗУ, ПЗУ, ППЗУ и ВЗУ (рис. 1)

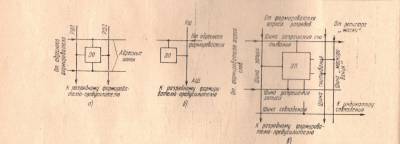

При традиционной организации СБИС ОЗУ, ПЗУ и ППЗУ применяется произвольный адресный поиск с помощью кода адреса, определяющего местоположение искомых дынных, причём время доступа к любому элементу памяти (ЭП) одинаково для всех ЭП. В состав этих СЕЙС ОЗУ на основе статических ЭП (рис. 2,а) входят матрицы ЭП с организацией m строк на n столбцов (причём ёмкость СБИС памяти составляет N = m×n бит) и блоки управления (БУ), которые позволяют производить поиск и ввод – вывод информации.

Рис. 1 – Классификация СБИС памяти по типу и способам хранения, поиска и ввода-вывода информации

Структурные схемы СБИС памяти разных типов включают блок ввода-вывода (либо отдельные схемы ввода и вывода), который позволяет после завершения поиска требуемой информации произвести её ввод-вывод.

Рис.2 – Статический (а) и динамический (б) ЭП для СБИС ОЗУ и ассоциативный ЭП (в) для СБИС АЗУ

2 ПРИНЦИПЫ ПРОЕКТИРОВАНИЯ СБИС ПАМЯТИ

2.1 Активно-пассивная организация питания СБИС памяти

Характерной особенностью организации современных СБИС памяти, позволяющей минимизировать потребляемую мощность, является активно-пассивный способ питания. Сущность этого способа заключается в том, что в режиме хранения информации часть или все БУ и матрица ЭП отключаются от источника питания. Если среди БУ есть последовательные схемы, т. е. БУ, используемые для ранения управляющей информации, то ток питания снижается до минимально допустимого уровня (пассивный режим). При обращении к СБИС памяти необходимые БУ и ЭП, определяемые способами поиск и ввода – вывода информации, автоматически переводятся в активное (рабочее) состояние. При этом их ток питания повышается до номинального уровня, что обеспечивает требуемое быстродействие. С точки зрения организации СБИС памяти это означает введение в структурную схему дополнительного блока мощных импульсных источников питания и дополнительных связей этого блока с остальными БУ.

Активно-пассивное питание матрицы ЭП СБИС на основе статических ЭП заключается в снижении тока хранения до уровня, необходимого для поддержания устойчивого бистабильного состояния ЭП.

При активно-пассивном питании ЗУ на ПЗС в режиме хранения понижается частота следования внешних тактовых сигналов. Для выполнения операций поиска и ввода – вывода тактовая частота повышается, и матрица ЭП переводится в режим повышенного потребления мощности и высокого быстродействия.

В некоторых СБИС памяти активно-пассивное питание реализуется путём разбиения матрицы ЭП на секции (рис.6).

Рис.6 – Структурная схема СБИС ОЗУ модели ТМS4164

Активно-пассивное питание блоков управления предусматривается в большинстве СБИС памяти. Встроенный генератор тактовых сигналов обеспечивает при обращении к СБИС подключение блоков управления к источнику питания в требуемой последовательности.

Применение СБИС памяти с активно-пассивным питанием позволяет сочетать пониженную потребляемую мощность в режиме хранения с высоким быстродействием при обращении и создавать ЗУ большого объёма (до 10ˆ6 - 10ˆ7 бит), не требующие дорогостоящего и громоздкого оборудования для принудительного охлаждения.

2.2 Принцип «базового кристалла» с перестраиваемой организацией

Большинство СБИС памяти имеет одноразрядную организацию, основные преимущества которой заключаются в том, что:

- необходимо минимальное количество внешних связей (выводов корпуса);

- обычно блок ввода-вывода работает на большую ёмкостную нагрузку внешних связей и потребляет значительную мощность;

- при организации ЗУ количество разрядов можно регулировать ступенями через один разряд;

- удобно построение специальных схем коррекции ошибок.

Экономически более оправданным является проектирование СБИС памяти на основе «базового кристалла» с изменяемой разрядной организацией. В зависимости от требований потребителя перестройка организации ведётся с помощью различных вариантов металлизации. По-видимому, наиболее целесообразно производить кристаллы СБИС памяти с фиксированными межсоединениями, а изменение разрядной организации осуществлять путём воздействия логических сигналов на специальный вход СБИС памяти.

2.3 Принцип структурно-топологической избыточности

С ростом степени интеграции и появлением новой элементной базы изменяется структурно-топологическая организация СБИС памяти. Под структурно-топологической организацией понимается взаимное расположение на кристалле БУ и матрицы ЭП.

Структурно-топологическая избыточность заключается в разделении матрицы ЭП на секции, увеличении аппаратных затрат на блоки адресного и разрядного управления и размещения этих БУ между секциями матрицы ЭП.

СБИС ОЗУ можно реализовать на основе динамических ЭП, в которых информация хранится на ёмкости МОП-структуры, а в качестве адресной шины используется базовая область многоэмиттерного биполярного транзистора. Высокая плотность размещения информации достигается путём вертикального расположения МОП-ёмкости хранения и n-p-n-биполярного переключательного транзистора. Так как базовая область n-p-n-транзистора, выполняющая роль адресной шины, имеет значительные распределённые сопротивление и паразитную ёмкость, то длина базы ограничена.

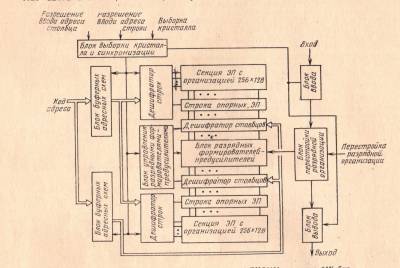

Таким образом, для уменьшения паразитных ёмкостей и омического сопротивления управляющих шин и повышения быстродействия СБИС памяти необходимо разделять матрицы ЭП на секции. Каждая секция может иметь собственные формирователи-предусилители, помещённые между секциями.

Особенностью структурных схем СБИС ОЗУ на основе динамических ЭП является наличие блока опорных ЭП. Для увеличения чувствительности и быстродействия разрядных формирователей-предусилителей увеличивается количество связей между матрицей ЭП и блоком опорных ЭП. Каждый формирователь-предусилитель, помимо мвязи с одной из секций, соединяется с двумя опорными ЭП.

Как уже указывалось, особенностью структурных схем СБИС ОЗУ на основе динамических ЭП является наличие блока опорных ЭП (рис.1).В ранних вариантах СБИС памяти использовался один общий бок опорных ЭП для нескольких секций матрицы. В более поздних разработках такой блок имеется в каждой секции матицы ЭП (рис.8).

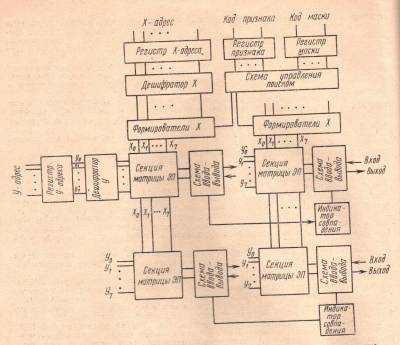

$IMAGE4$

Рис.8 – Структурная схема СБИС ОЗУ ёмкостью 16 К бит с дополнительными управляющими мультиплексорами

В некоторых СБИС памяти помимо дополнительных опорных ЭП, формирователей-предусилителей и адресных формирователей, применяются специальные управляющие мультиплексоры.

Применение структурно-топологической избыточности позволяет получить СБИС памяти с высокими техническими характеристиками, однако при этом степень интеграции ограничена. Поэтому в настоящее время наметилась тенденция к применению функциональной интеграции, в частности, трёхмерных интегральных структур ЭП и ЭП с многоуровневым хранением информации. Повышение информационной ёмкости СБИС памяти возможно при многоуровневом хранении информации. При этом необходима отработка технологии и структурной организации СБИС на основе ЭП с многоуровневым хранением информации.

2.4 Многофункциональное использование связей матрицы с блоками управления

При проектировании СБИС памяти широко применяется принцип многофункционального использования связей матрицы с БУ. Например, разрядные шины в матрицах ЭП СБИС ОЗУ, ПЗУ, ППЗУ используются одновременно для выборки необходимого разряда в стоке ЭП и записи – считывания в него информации.

Многофункциональное использование связей матрицы ЭП с БУ позволяет сократить число управляющих шин и, тем самым, повысить плотность размещения информации. Однако при этом уничтожаются требования к электрическим параметрам БУ и возникает проблема коммутации управляющих шин к различным БУ.

2.5 Способы неавтономной и автономной организации хранения

Информация в ЗУ может храниться автономно и неавтономно. Сущность автономного хранения заключается в том, что центральный процессор управляет лишь выборкой необходимой информации и её обработкой. При этом не требуется управление хранением информации, что позволяет повысить производительность ЭВМ. Соответственно при неавтономной организации хранения необходимо подавать в ЗУ сигналы управления хранением.

Неавтономная организация хранения в современных СБИС памяти на основе динамических ЭП чаще всего выполняется с помощью внешней адресной регенерации. При этом регенерация осуществляется в последовательно адресуемых частях матрицы ЭП. В течение периода регенерации информация восстанавливается во всех ЭП.

Существует несколько способов внешней адресной регенерации и требуется соответствующее число типов интегральных схем управления регенерацией.

Внешняя адресная регенерация привлекает разработчиков, потому что для её реализации не требуется усложнения структурной схемы СБИС памяти. В некоторых ЗУ небольших микропроцессорных систем наличие времени занятости не играет особой роли, так как циклы регенерации приводятся в те интервалы времени, когда обращения к памяти не требуется.

Внешняя безадресная регенерация также применяется при неавтономной организации хранения информации, когда СБИС памяти позволяет восстанавливать информацию одновременно во всех ЭП матрицы либо во всех СБИС, на которых построено ЗУ.

Автономная организация хранения применяется в СБИС памяти на основе динамических ЭП, которые называют «квазистатическими» или «псевдостатическими».

Для внутренней безадресной регенерации в структурную схему вводятся специальные блоки генераторов «подкачки», которые предотвращают потерю информации в ЭП.

Внутренняя безадресная регенерация применяется в СБИС памяти на основе моностабильных ЭП. Для уменьшения потребляемой мощности применяется активно-пассивная организация питания генератора опорного напряжения с периодом 12мс.

Проектирование СБИС памяти на основе динамических ЭП с внутренней адресной регенерацией в настоящее время, по-видимому, является наиболее реальным Матрица СБИС памяти не претерпевает каких-либо изменений и сохраняет высокую плотность размещения информации.

СБИС ОЗУ с автономным хранением информации являются весьма перспективными, так как позволяют совместить высокую степень интеграции СБИС памяти на основе динамических ЭП с автономностью хранения информации, присущей СБИС памяти других типов.

3 СПОСОБЫ ВЫБОРКИ ИНФОРМАЦИЯ И ОРГАНИЗАЦИЯ СБИС ПАМЯТИ

По способу поиска информации СБИС памяти можно разделить на СБИС памяти с адресным, безадресным и комбинированными способами, а по способу ввода-вывода – на СБИС памяти с последовательным, параллельным и комбинированным вводом–выводом

3.1 Адресный поиск

Произвольный адресный поиск выполняется с помощью дешифраторов строк и столбцов ЭП (адресных и разрядных дешифраторов).

При матричной адресации ЭП также участвуют в операции поиска, так как на них выполняется операция совпадения. Все ЭП матриц объединяются общей управляющей шиной, по которой производится запись или считывание информации.

При словарной адресации матриц, которая чаще всего применяется в СБИС памяти, адресная строка ЭП (слово), а затем с помощью дешифратора столбцов выбирается один или несколько разрядов строки. Каждому столбцу ЭП соответствует свой разрядный формирователь-предусилитель.

Последовательный адресный поиск чаще всего применяется в СБИС памяти на основе сдвиговых регистров (например, ПЗС-регистров). Для сдвига информации к схемам ввода-вывода в ЗУ на ПЗС имеется специальный тактовый вход (ТИ).

Комбинированный произвольно-последовательный поиск применяется в последних разработках СБИС памяти. В частности, в ЗУ на ПЗС применяется произвольный поиск регистра и последовательный поиск в самом регистре.

В СБИС памяти с комбинированным поиском применяются специальные способы адресации: двойная и ортогональная.

Двойная адресация реализуется, если каждая строка ЭП или один ЭП строки будут связаны со всеми ЭП следующей строки или с одним ЭП следующей строки.

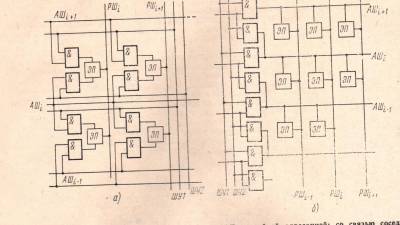

На рис.10, а представлен фрагмент матрицы ЭП, в котором к каждому ЭП подсоединены дополнительные схемы И, связывающие соседние строки ЭП и соседние ЭП в строках, а на рис.10, б – лишь соседние строки ЭП.

Рис.10 – Фрагменты схемы матрицы ЭП с двойной адресацией: со связью соседних ЭП (а) и со связью соседних строк ЭП (б)

Адресные шины (АШ) и шины управления (ШУ, ШУ2) позволяют считывать информацию из ЭП по разрядным шинам (РШ) в требуемой последовательности.

Ортогональная адресация, реализуемая объединением соседних строк ЭП с помощью специальных адресных формирователей, позволяет производить поиск и ввод-вывод столбцов ЭП (разрядных сечений) матрицы. В этом случае выборка ортогональна по отношению к словарной выборке (в виде строки). В некоторых случаях подобная организация может увеличивать эффективность СБИС памяти.

3.2 Безадресный поиск

Безадресный поиск информации в настоящее время реализован в СБИС АЗУ и ЗУ обратного магазинного типа.

Ассоциативный поиск по совпадению заключается в том, что k-разрядный признак записывается в специальный регистр входного признака для формирования кода опроса. В процессе поиск происходит сравнение признака опроса с признаками всех N слов, хранящихся в АЗУ. Результат совпадения фиксируется в блоке индикаторов совпадения и шифрации адреса.

Ассоциативный поиск по числовому критерию используют в некоторых случаях для обработки упорядоченных массивов информации, в которых каждому слову с меньшим номером соответствует меньшее значение признака, а слову с большим номером – большее или совпадающее значение.

Существует несколько способов организации СБИС АЗУ для выполнения ассоциативного поиска:

1) последовательный по словам и параллельный по разрядам,

2) параллельный по словам и последовательный по разрядам,

3) параллельный по словам и разрядам,

4) последовательный по словам и разрядам.

Поиск в ЗУ магазинного типа выполняется следующим образом: матрица ЭП заполняется информацией последовательно, начиная с первого ЭП или слова (нескольких ЭП). Информация в ЗУ обратного магазинного типа может записываться только в первый регистр, причём при вводе информации из последнего регистра удаляется, а при выводе последние разряды заполняются нулями.

3.3 Комбинированный адресно-ассоциативный поиск

При проектировании СБИС памяти перспективным является применение комбинированного адресно-ассоциативного поиска. Этот способ поиска позволяет сочетать большую информационную ёмкость и минимальное число выводов корпуса, характерные для СБИС ОЗУ, с возможностью ускоренного поиска в СБИС АЗУ.

Один из способов комбинированного поиска заключается в том, что матрица ЭП разбивается на секции с матричной организацией, имеющие общие управляющие шины, и для адресации столбцов ЭП используются только (k-1)-разрядный адресный код вместо k-разрядного, а по оставшимся адресам хранятся ассоциативные признаки (рис.11).

Рис. 11 – Структурная схема ЗУ с произвольным адресным и ассоциативным поиском

Возможно также сочетание последовательного адресного и ассоциативного поиска. Блок управления ассоциативным поиском выполняет поиск признака модуля и зон. При наличии совпадения с входным признаком производится последовательный поиск в зоне. Преимущество описанного в ЗУ на ПЗС состоит в минимальном количестве тактовых сигналов (ТИ1 и ТИ2), которые позволяют сочетать высокую скорость поиска и ввода – вывода при обращении к ЗУ с малой потребляемой мощностью в режиме хранения.

3.4 Последовательный и параллельный ввод – вывод

В современных СБИС памяти применяются два способа ввода-вывода информации: последовательный одноразрядный ввод – вывод, используемый в СБИС памяти с одноразрядной организацией и параллельный многоразрядный ввод – вывод в СБИС с многоразрядной организацией.

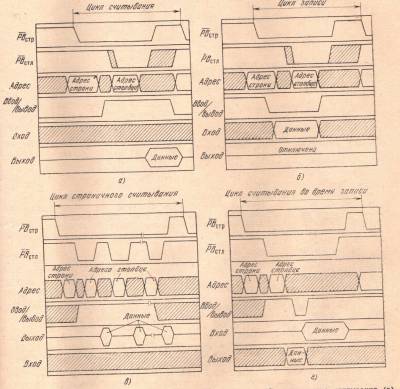

Последовательный ввод–вывод может быть однотактным с произвольной сменой адреса искомого одноразрядного слова и многотактным (страничным) для ввода–вывода «страниц» информации, расположенной в ЭП с соседними адресами. На рис. 13, а и б приведены временные диаграммы работы СБИС памяти при однотактном выводе (считывании) и вводе (записи) соответственно, а на рис.13, в – при многотактном (страничном) вводе-выводе.

Наиболее просто страничная выборка реализуется в СБИС ЗУ на ПЗС. При последовательной организации СБИС размер «страницы» составляет 256-4096 бит.

Для СБИС ОЗУ разработаны специальные способы ускоренного страничного ввода – вывода. Например, в течение цикла считывается информация из произвольной строки ЭП, фиксируется блоком предусилителей – формирователей и записывается в дополнительный регистр. Последовательно сдвигая информацию от разряда к разряду, можно вывести «страницу» объёмом, например 64 бита.

Рис.13 – Временные диаграммы циклов считывания (а), записи (б), страничного считывания (в), считывания во время записи (г) в СБИС ОЗУ ёмкостью 16К бит

Параллельный ввод – вывод m-разрядных слов ускоряет процесс обмена с ЦП и между различными уровнями иерархической памяти ЭВМ, т.е. повышает быстродействие ЗУ. При этом используется как однотактный, так и многотактный параллельный ввод – вывод информации.

Мультиплексированный ввод информации в СБИС памяти играет особую роль при минимизации габаритов ЗУ, занимающих до 60-90% физического объёма ЭВМ. Габариты ЗУ определяются информационной ёмкостью применяемых СБИС памяти и количеством выводов корпусов. Поэтому при проектировании СБИС памяти, помимо увеличения информационной ёмкости, необходимо предусмотреть многофункциональное использование выводов корпуса.

Структурная организация некоторых современных СБИС ОЗУ позволяет вводить адресную информацию с помощью мультиплексирования. Организация ввода адресов позволяет размещать в одинаковых, например, в 16-выводных корпусах СБИС ОЗУ ёмкостью 4 и 16 Кбит. Причём разводка корпусов может быть почти одинаковой.

Таким образом, использование комбинированных способов выборки повышает быстродействие СБИС памяти и универсальность их применения, а мультиплексированный ввод адресов увеличивает информационную емкость ЗУ.

4 ПЕРСПЕКТИВЫ РАЗВИТИЯ СБИС ПАМЯТИ И ЗУ НА ИХ ОСНОВЕ

В настоящее время можно выделить две концепции проектирования СБИС памяти и ЗУ на их основе.

Первая концепция базируется на достаточно «жёстком» разграничении функций арифметико-логической обработки информации и хранения выборки обрабатываемой и управляющей информации между процессорными СБИС и СБИС памяти. Организация СБИС памяти разных типов при этом остаётся «традиционной», и СБИС содержит соответственно связанные между собой матрицу ЭП и БУ.

Второй концепцией, отражающей стремление функции обработки и хранения в единой универсальной ячейке, является создание однородных вычислительных сред.

4.1 Проектирование ЗУ на основе СБИС памяти с «традиционной» организаций и многофункциональных интерфейсных БИС

При проектировании ЗУ, состоящего из нескольких СБИС памяти, расположенных, например, на печатной плате, для управления этими СБИС и связи с ЦП специально разрабатываются функциональные интерфейсы БИС (контроллеры).

С помощью контроллера выполняются следующие операции управления ЗУ:

передача информации по универсальной магистрали для хранения в ЗУ;

вывод информации из ОЗУ для передачи в любое из устройств ЭВМ по универсальной магистрали;

непосредственный ввод-вывод информации из арифметико-логического блока ЭВМ в ОЗУ;

выполнение регенерации в СБИС ОЗУ.

К недостаткам некоторых типов СБИС памяти можно отнести потерю информации при отказе источника питания.

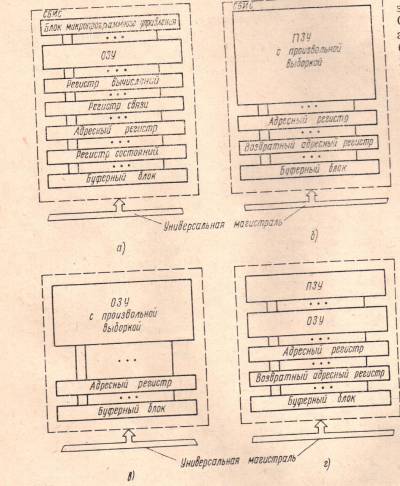

На рис.16 приведена схема контроллёра, который может выполнять подключение аварийного источника питания и аварийную регенерацию.

$IMAGE8$

Рис. 16

4.2 Проектирование цифровых систем на основе однородных вычислительных сред

Элементарная ячейка однородной вычислительной среды (ОВС) способна хранить информацию и выполнять набор арифметических и логических операций.

Достоинства вычислительных систем на основе ОВС состоят в том, что матрицы ячеек ОВС универсальны и позволяют достаточно легко реализовать тестирование и диагностику ошибок, а также увеличивать вычислительную мощность систем путём наращивания. С помощью ОВС можно осуществлять распараллеливание вычислительного процесса и тем самым повышать быстродействие системы. Легко также строятся цифровые системы с повышенной работоспособностью и надёжностью за счёт введения избыточных ячеек.

4.3 Новые подходы к структурной организации СБИС памяти и ЗУ на их основе

Одной из концепций структурной организации СБИС памяти и ЗУ на их основе, занимающие промежуточное положение между ОВС и СБИС памяти является объединение в различных сочетаниях на одном кристалле СБИС памяти разных типов либо с различной организацией.

СБИС, включающая ПЗУ с обычной словарной адресацией, ПЗУ и двойной адресацией и регистры управления и ввода – вывода, служит для выполнения операций сложения – вычитания и может быть выполнена на одном кристалле.

Существует ещё одна концепция организации СБИС памяти: основную часть кристалла занимает матрица ЭП, остальную – логические блоки и блоки интерфейса для реализации комбинированных способов поиска и ввода – вывода информации. Это не что иное, как «разумная» память, отличающаяся гибким доступом.

На рис.17 представлена СБИС памяти с расширенными функциональными возможностями: процессорная СБИС (а), СБИС хранения управляющей информации (б), СБИС хранения обрабатываемой информации (в), СБИС для ввода-вывода информации.

Рис.17

Таким образом, СБИС памяти с расширенными функциональными возможностями могут содержать ОЗУ, ПЗУ, ППЗУ в различных сочетаниях и отдельны регистры для выполнения арифметико-логических операций, буферные интерфейсные схемы для работы на универсальные магистрали и т.д.

ЗАКЛЮЧЕНИЕ

Обзор выпускаемых промышленностью и разрабатываемых зарубежными фирмами СБИС памяти различных типов показывают, что существуют значительное количество вариантов структурной организации СБИС. Сравнение этих вариантов позволяет выделить некоторые перспективные принципы проектирования СБИС памяти различных типов:

активно-пассивная организация питания матрицы ЭП и боков управления;

применение «базового» кристалла с электрически перестраиваемой организацией;

структурно-топологическая избыточность;

«автономность» организации хранения информации;

многофункциональное использование связей матрицы ЭП и блоков управления и выводов корпуса СБИС.

Наиболее перспективной является организация СБИС памяти с расширенными функциональными возможностями, отличающихся высокой информационной ёмкостью.

Использование комбинированных способов поиска ввода – вывода и многофункциональность связей повышает универсальность применения СБИС памяти, уменьшает номенклатуру типов и снижает стоимость хранения одного бита информации. Упрощается также переход к созданию цифровых систем на базе однородных вычислительных систем.

Использованный источник для данного конспекта: статья Алексеенко А.Г., Лапшинского В.А. Современное состояние, особенности проектирования и перспективы развития сверхбольших ИС памяти.

Список литературы

1. Электроника, 1978, v. 51, № 13, с. 108.

2. Пат. 4008460 (США), НКИ 340-172. 5, 1977.

3. Пат. 4004067 (США), НКИ 340-173, 1976.

4. Электроника, 1977, т. 50, №16, с. 34.

5. Young S. Uncompromising 4 K static RAM runs fast on little power. – Electronics, 1977, v. 50, № 10, p. 99–103.

[color=blue]

Источник: http://статья Д. т. н. Алексенко и А.Г. Лапшинский В.А. |

Категория: Конспекты (курсы КП и ПК) | Добавил: Yana (25.05.2013)

| Автор: Мисюченко Яна

|

| Просмотров: 1194

| Рейтинг: 0.0/0 |

Добавлять комментарии могут только зарегистрированные пользователи. [ Регистрация | Вход ] |

|