| Статистика |

Онлайн всего: 1 Гостей: 1 Пользователей: 0 |

|

"Расширение функциональных возможностей сверхБИС памяти"

Национальный Исследовательский Ядерный Университет

«Московский Инженерно-Физический Институт»

Факультет «Автоматики и электроники»

Кафедра № 27 «Микро- и наноэлектроника»

Компьютерный практикум: применение ПК (КП-13)

Расширение функциональных возможностей сверхБИС памяти

Выполнила:

Студентка группы А4-09

Мухамадуллина С.Р.

Преподаватель:

Доцент Лапшинский В. А.

Москва 2013

Глоссарий

ЗУ – запоминающееся устройство

ЦП – центральный процессор

КПП – компоновочное пространство памяти

СверхБис – сверх-большая интегральная схема

Оглавление

Введение.................................................................................................................................3

Компоновочное пространство памяти и его основные параметры.................................................3

Параметры компоновочного пространства...................................................................................4

Эффективное быстродействие компоновочного пространства памяти на основе сверхБИС ТОП....6

Информационный объем компоновочного пространства памяти....................................................7

Мощность, рассеиваемая в компоновочном пространстве памяти.................................................9

Заключение............................................................................................................................11

Литература..............................................................................................................................12

Введение

Одной из основных проблем иерархических систем памяти является проблема повышения скорости обмена информацией между запоминающими устройствами (ЗУ), центральным процессором (ЦП), периферийными устройствами и внутри иерархии ЗУ[1,2].

Цель работы состоит в том, чтобы оценить основные параметры ЗУ (быстродействие, информационный объем, потребляемая мощность) на основе сверхБИС памяти с расширенными функциональными возможностями и сравнить с параметрами аналогичных ЗУ на основе микросхем памяти с типовой организацией [3].

Для проведения оценок разработана и исследована модель компоновочного пространства памяти (КПП). Из анализа модели КП устройств ЭВМ могут быть выявлены зависимости между электрическими, конструктивными и архитектурными параметрами элементной базы и аналогичными параметрами КП в целом.

Компоновочное пространство памяти и его основные параметры

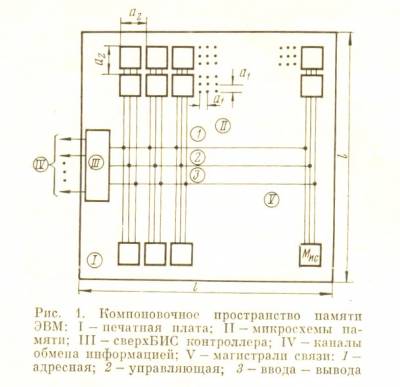

Элементная база компоновочного пространства. Оценим и сравним параметры КПП для типичных способов обмена информацией: выборки данных с произвольной сменой адресов (ПВ), блочной или страничной выборки (БВ) [1] и ассоциативной выборки по признакам (АВ) [5], полагая, что обмен информацией КПП с другими устройствами ЭВМ происходит по магистралям адресов, управления и ввода – вывода данных, объединяющих выводы корпусов микросхем памяти (рис.1).

СверхБИС с типовой организацией памяти (сверхБИС ТОП) имеют два режима ПВ: ввода или вывода информации. Для организации БВ или АВ необходимо соответствующее количество циклов ПВ, каждый из которых сопровождается подачей соответствующего адреса и управляющих сигналов [3].

Если в сверхБИС с расширенными функциональными возможностями или сверхБИС суперкомпонентов памяти (СКП) предусмотрен режим БВ, то для выполнения цикла выборки необходимо задать адрес «начального» бита страницы информации. Дальнейший перебор адресов и ввод – вывод данных происходит автоматически под управлением специальных встроенных схем управления. В данном случае нет необходимости в многократной дешифрации адресов, поэтому быстродействие СКП в режиме БВ

возрастает на 30÷50% [3]. В сверхБИС СКП цикла АВ вводится

ассоциативный признак и производится его сравнение с признаками, хранящимися в ассоциативной части накопителя СКП и выборка соответствующего блока информации.

В таком случае, отсутствие многократных передач управляющих сигналов со стороны ЦП является отличительной особенностью режимов БВ и АВ и сверхБИС СКП.

Дополнительные возможности повышения скорости обмена – это перестраиваемость разрядности ввода – вывода сверхБИС СКП.

Параметры компоновочного пространства

Время цикла КПП в режиме обмена информацией представляет собой сумму времени цикла выборки сверхБИС памяти и времени прохождения сигналов по магистрали связи между ЦП и ЗУ.

Необходимо сделать n передач адресной строки и управляющей информации и соответствующую передачу данных для ввода и вывода бита. Информационный объем КПП определяется площадью печатной платы Sп, количеством выводов в корпусах микросхем (A) и емкостью сверхБИС памяти Nис*.

Минимальные размеры многовыводного корпуса получаются при равномерном расположении выводов с шагом a1 по всей площади дна корпуса [4]. В случае, если корпус квадратный, то шаг установки корпусов (a2) и площадью корпуса (Sk) определяются (рис.1) a2 = a1 и Sп = a12А.

В случае компактной установки корпусов число корпусов на плате равно

Мис = Sп/ a12А,

емкость ЗУ:

Nзу = Мис× Nис.

Мощность, которая выделяется в КПП равна сумме мощности рассеиваемой микросхемами , находящимися в пассивном состоянии и в активном режиме выборки, и мощности, необходимой для передачи сигналов по магистралям с согласованными нагрузками.

Эффективное быстродействие компоновочного пространства памяти на основе сверхБИС ТОП

Выражения для эффективного времени выборки сверхБИС памяти в КПП в режимах ПВ, БВ и АВ:

tп.э = tб.э = tв + (n+1)tс,

tа.э = tср + (2+L/K)tп.э.

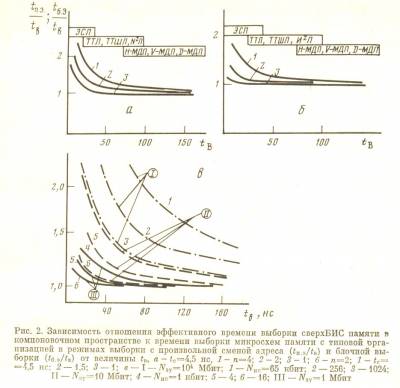

Удобным критерием эффективности использования быстродействия микросхем памяти в КПП являются отношения tп.э/tв и tа.э/tср. На рис. 2 представлены зависимости tп.э/tв и tб.э/tв, и их анализ показывает, что наиболее существенны потери в магистралях для биполярных сверхБИС памяти, применяемых для построения быстродействующих ЗУ.

Существует два варианта организации ассоциативной выборки. В первом случае в ЗУ хранится небольшое количество блоков данных (L/K<<1), поэтому

tа.э =tб.э = tп.э.

Во втором случае, если память разбита на страницы небольшого объема (L/K 1), то цикл будет определяться временем

tа.э = tср + 3tп.э.

Информационный объем компоновочного пространства памяти

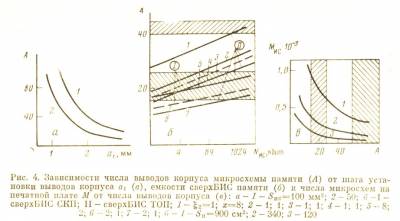

При заданных параметрах технологического процесса изготовления КПП, т.е. при экономически оправданных значениях Nис , Sп , a1 информационный объем КПП Nзу зависит от способа организации сверхБИС памяти, в частности от количества выводов корпусов микросхем (А)

А = Аа + Ас + Ар + А вв+Ап,

На рис. 4, б представлены зависимости числа выводов корпуса микросхемы памяти от ее информационного объема и вариантов структурной организации.. Анализ данных показывает, что необходима минимизация числа выводов корпуса путем мультиплексированного ввода адреса, совмещения выводов записи - считывания и уменьшения разрядности ввода-вывода. Максимальная разрядность ввода-вывода ограничена на уровне x≤ 8. Если увеличивается допустимая разрядность ввода – вывода x> 8, то возможен однотактный ввод адреса, что позволяет оптимальным образом использовать микросхемы в ЗУ различного типа и архитектуры.

Следовательно, большая часть выводов микросхем памяти требуется для ввода адреса и многоразрядного ввода-вывода данных. Ясно, что отсутствие мультиплексирования и применение многоразрядных магистралей ввода-вывода позволяет вести параллельный обмен информацией, что повышает эффективное быстродействие ЗУ и производительность ЭВМ.

Повышение плотности компоновки сверхБИС памяти на печатной плате (рис. 4) приводит к уменьшению влияния числа выводов корпусов микросхем на емкость ЗУ. Это значит, что при незначительном сокращении объема можно повысить эффективное быстродействие памяти.

Мощность, рассеиваемая в компоновочном пространстве памяти

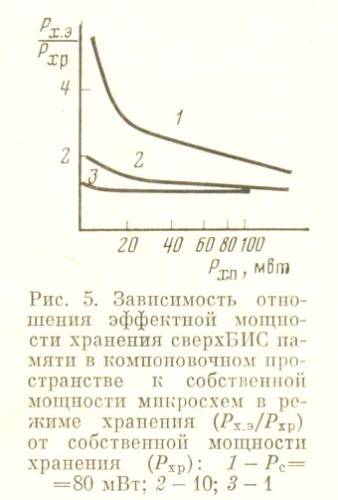

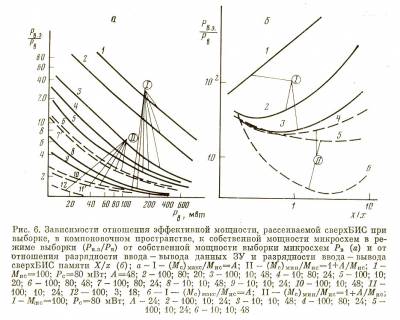

Отношения Рх.э /Рхр и Рв.э/Рв являются удобным критерием относительного вклада элементов согласования в общую мощность, рассеиваемую в КПП.

На рис. 5 следует, что при Рхр≤ 50мВт существенный вклад в Рх.э вносит рассеивание мощности на согласующих резисторах. Поэтому по мере уменьшения Рхр необходимо снижать амплитуду передаваемых по магистралям сигналов.

На рис. 6 представлены зависимости Рв.э/Рв от мощности Рв для различных сочетаний параметров сверхБИС памяти, имеющих , и параметров КПП. Эти зависимости дают также возможность оценить вклад потерь на передачу сигналов по магистралям при блочной и ассоциативной выборке, когда длительное время большая часть микросхем КПП находится в рабочем состоянии.

Надежность работы КПП может быть повышена путем параллельной работы нескольких блоков памяти на один общий канал обмена, а также при использовании техники корректирующих кодов.

Анализ выражений для эффективной мощности ЗУ с различной архитектурой показывает, что для каждого из вариантов существует оптимальная разрядность ввода-вывода для сверхБИС памяти. Таким образом, использование сверхБИС СКП с перестраиваемой разрядной

организацией в ЗУ с различной архитектурой улучшает параметры КПП по потребляемой мощности.

Заключение

Оценка параметров компоновочного пространства памяти ЭВМ на основе сверхБИС памяти емкостью более 4 кбит позволяет сделать следующие выводы.

1. Использование сверхБИС суперкомпонентов памяти позволяет в 2-3 раза повысить скорость обмена информацией при блочной и ассоциативной выборке по сравнению со сверхБИС с типовой организацией памяти за счет уменьшения числа передач сигналов по управляющим магистралям и усовершенствования организации сверхБИС памяти, допускающих специальные режимы выборки информации.

2. Увеличение числа выводов в корпусах для сверхБИС памяти будет стимулировать расширение их функциональных возможностей. Это приведет к снижению стоимости разработки и построения обширного класса полупроводниковых ЗУ на минимальном количестве типов универсальных сверхБИС суперкомпонентов памяти.

3. Для повышения экономичности компоновочного пространства памяти в режиме хранения и выборки информации необходимо использовать в выходных каскадах ЦП буферные схемы с тремя состояниями, увеличивать число объединяемых общими магистралями микросхем памяти.

4. Дополнительные функции сверхБИС памяти: блочная и ассоциативная выборка информации, перестраиваемая разрядность ввода адреса и ввода-вывода данных, организация встроенного активно-пассивного питания.

Литература

1. Карцев М.А. Архитектура цифровых вычислительных машин. М.: Наука, 1978.

2. Смирнов Р.В. Микроэлектроника и полупроводниковые приборы / Под ред. Васенкова А.А. и Федотова Я.А., 1978. №3.- C. 117.

3. Лапшинский В.А.Микроэлектроника, 1977. т.8. №4.- C. 90.

4. Чунаев В.С. Микроэлектроника, 1977. т.6. № 2.- C. 299.

5. Балашов Е.П. и др. Многофункциональные регулярные вычислительные структуры. М.: Советское радио, 1978.- C.77.

6. Шагурин И.И. Микроэлектроника, 1978. т.7. №2.- C. 99.

7. Журавлев Ю.П., Котелюк Л.А., Циклинский Н.И. Надежность и контроль ЭВМ. М.: Советское радио, 1978.- C. 152.

Источник: http://статья А.Г.Алексеенко, В.А. Лапшинский |

Категория: Конспекты (курсы КП и ПК) | Добавил: SvetlanaM93 (26.05.2013)

| Автор: Мухамадуллина С.Р. гр. А4-09

|

| Просмотров: 531

| Рейтинг: 0.0/0 |

Добавлять комментарии могут только зарегистрированные пользователи. [ Регистрация | Вход ] |

|