Национальный исследовательский ядерный университет «МИФИ»

Факультет: «Автоматика и электроника»

Кафедра: «Микро- и наноэлектроника»

Предмет: «Компьютерный практикум˗13»

Сравнительный обзор запоминающих элементов

с инжекционным питанием

и субсистемы памяти на их основе

Группа: А4-11

Подготовил: Дергачев А.С..

Преподаватель: доц. Лапшинский В.А.

Москва 2013

Глоссарий

Транзисторы – радиоэлектронный компонент из полупроводникового материала, обычно с тремя выводами, позволяющие входным сигналам управлять током в электрической цепи.

Матрица памяти – запоминающее устройство, хранящее информацию в виде направления намагниченности небольших ферритовых сердечников.

Электрическая схема – документ содержащий в виде условных изображений или обозначений составные части изделия, действующие при помощи электрической энергии и их взаимосвязи [2].

МДП – транзистор – транзисторы с изолированным затвором.

Интегральные субсистемы памяти – приборы, выполняющие типовые функции, наращивающие в широком диапазоне число разрядов, имеющие ограниченное число внешних связей.

Оглавление

ВВЕДЕНИЕ……………………………………………………………………….…..…..4

1. ЗЭ С Р-П-Р нагрузочными устройствами…………………………………….…..5

2. ЗЭ «сверхинтегрированного» варианта…………………………………….…....7

3.ЗЭ с двунаправленными ключами………………………………….…................11

ЗАКЛЮЧЕНИЕ…………………………………………………………………..……12

ИСТОЧНИКИ ИНФОРМАЦИИ……………………………………………………….12

Введение

Одной из важнейших задач современной микроэлектроники является разработка интегральных субсистем памяти большой емкости (≥1 кбит), обеспечивающих высокое быстродействие при достаточно малом потреблении мощности. До последнего времени субсистемы памяти такой емкости создавались на основе МДП – транзисторов, однако они не обеспечивали высокого быстродействия. После того как в 1972 году были разработаны схемы с инжекционным питанием, которые занимают почти такую же площадь на кристалле. Как и системы на МДП – транзисторах, стало возможным на их основе создавать субсистемы памяти большой емкости и достаточно высокого быстродействия [2].

1. ЗЭ с р-п-р нагрузочными транзисторами

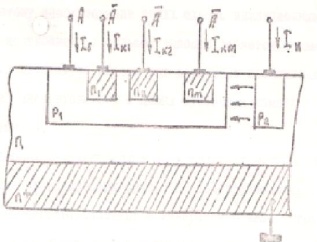

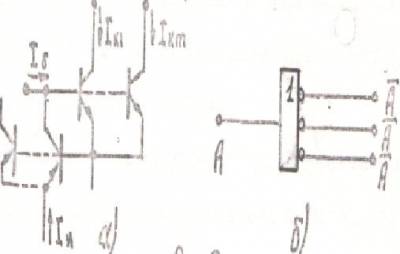

На рис. 1 показана физическая структура схемы с инжекционным питанием (отдельный инвертор), а на рис. 2 и 3 ее эквивалентные схемы

Рис. 1

Рис. 2

Рис. 3

Схема ИЛ (инжекционной логики) состоит из вертикального п-р-п транзистора и совмещенного с ним продольного р-п-р транзистора. Эмиттером р-п-р транзистора служит дополнительная р-область (инжектор), базой – общая для многих р-п-р транзисторов подложка или эпитаксиальная пленка п-типа, коллектором – база п-р-п транзистора. Общая область п-типа со «скрытым» п+ слоем служит также и общим эмиттером для расположенных на кристалле п-р-п транзисторов. Схемы ИЛ (инжекционной логики) обеспечивают такие параметры: (р٭t₃) = (0,35÷1.0) пДж при потребляемой мощности Р=1 нВт:1 мкВт и занимают площадь (500÷1500) мкм². Поэтому использование таких систем с инжекционным питанием для построения ЗУ большой емкости является весьма перспективным. В литературе описан ряд вариантов инжекционных запоминающих элементов (ЗЭ) и целых субсистем с инжекционным питанием.

Прообразы инжекционных ЗЭ

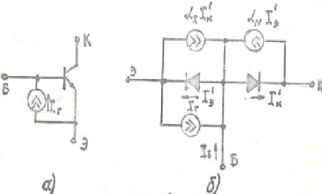

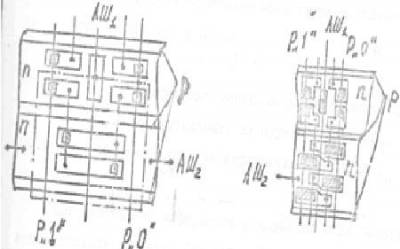

Прообразом инжекционных ЗЭ явились схемы ЗЭ с р-п-р нагрузочными транзисторами (рис. 4). Переключающие транзисторы Т3, Т4 триггера работают в инжекционном режиме, а транзисторы Т5,Т6 в нормальном либо в инверсном режиме, осуществляя развязку между схемой бистабильной ячейки с разрядными шинами Р ʺIʺ и Р ʺОʺ. Р-п-р транзисторы Т1, Т2 с общей базой и эмиттером выполняют роль резисторов нагрузки. Использование р-п-р нагрузочных транзисторов дает возможность достичь малой мощности рассеивания по постоянному току. При этом минимальный ток, потребляемый ЗЭ, определяется коэффициентом передачи нагрузочного р-п-р транзистора и уровнем тока, при котором коэффициент усиления инверсноработающего транзистора Т3 (Т4) – βI упадёт до I. Два варианта топологии такого ЗЭ показаны на рис. 5а и 5б. Площадь, занимаемая ЗЭ на кристалле, составляет 8700мкм². Параметры ЗЭ в режиме записи и считывания 10нсек. и 80нсек., соответственно Достоинством ЗЭ с р-п-р нагрузочными транзисторами является то, что он может быть сформирован с использованием обычной планарно-эпитаксиальной технологии и однослойной металлизации. У этой ячейки можно отметить такие недостатки: во-первых, при перезаписи транзисторы Т5 (Т6), работающие в режиме эмиттерных повторителей, потребляют большой ток, поэтому запись неэкономична. Во-вторых, наличие изолирующих р-областей увеличивает площадь, занимаемую ЗЭ.

Рис. 4

Рис. 5

Пути совершенствования ЗЭ

Дальнейшее совершенствование такого ЗЭ идет тремя путями:

1. Усовершенствованием топологии для более простой организации матрицы памяти и увеличение плотности компоновки.

2. Применением новых технологических методов также с целью увеличения плотности компоновки и увеличения фактора качества схем (1/рt₃).

3. Усовершенствованием электрической схемы ЗЭ.

2. ЗЭ «сверхинтегрированного» варианта

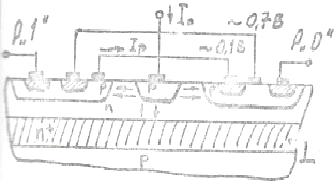

На рис. 6 приведен поперечный разрез кристалла.

Рис. 6

Принцип работы «сверхинтегрированного» ЗЭ аналогичен принципу работы ЗЭ с р-п-р нагрузочными транзисторами. В режиме хранения информации один из транзисторов Т3 (Т4) открыт и насыщен, а другой – находится в отсечке. Так как транзисторы Т3 (Т4) работают в инверсном режиме, то для обеспечения работоспособности бистабильной ячейки необходимо выполнение условия βi(αpIo)>1 где:

αp – коэффициент передачи р-п-р транзисторов

Io – ток, вытекающий из адресной шины АШ

ЗЭ этого типа могут хранить информацию при токах I0 ~ 100нА и менее.

При считывании информации в адресные шины выборки подаются положительные импульсы. Ток через ЗЭ увеличивается (на два, три порядка), что позволяет уменьшить времена перезарядки паразитных емкостей разрядных шин. Пусть, например, транзистор Т3 (Т4) открыт, тогда при воздействии импульса выборки переход эмиттер-база транзистора Т5 смещается в прямом направлении. В разрядную шину РʺОʺ втекает ток, который повышает ее потенциал до Uпор – порога отпирания схемы считывания. Информацию можно зафиксировать с помощью схемы, которая чувствительна к разности потенциалов разрядных шин РʺIʺ и РʺОʺ.

При записи напряжение на адресной шине повышается, в тоже время на одной из разрядных шин напряжение понижается. Если например транзистор Т3 открыт, а запись ведется по шине РʺIʺ, тогда включается транзистор Т6, и потенциал базы Т4 определяется потенциалом разрядной шины. В результате транзистор Т3 выключается и открывается транзистор Т4. Время задержки сигнала при считывании мало (tсч~10÷15нс)благодаря быстрому включению тиристорной структуры, образованной транзисторами Т1-Т5. Однако вследствие этой же тиристорной структуры запись информации в ЗЭ затруднена. Управляющие схемы должны обеспечивать достаточно большие значения токов через ЗЭ в процессе записи.

Вариант ЗЭ с уменьшенным током записи (при заданной скорости записи). Для уменьшения тока записи вводятся последовательные сопротивления в коллекторных цепях транзисторов Т5(Т6) (рис 7а). Распределенное сопротивление rк создается за счет формирования ЗЭ в более высокоомной эпитаксиальной пленке (рис.7б).

Рис. 7

Реализация словарно-организованной матрицы памяти

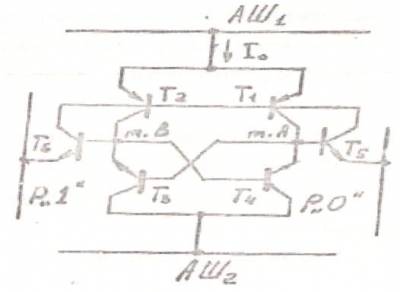

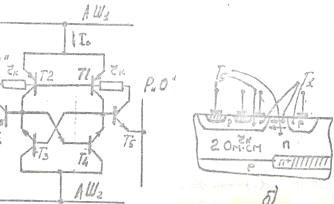

На базе «сверхинтегрированных» ЗЭ можно реализовать словарно-организованную матрицу памяти (рис.8 и 9).

Рис. 8

рис. 9

Все ЗЭ одного слова располагаются в изолированной области п-типа, имеющей вид полосы. При этом ЗЭ занимает на кристалле площадь 2500мкм² (при минимальной ширине металлизации 5 мкм и размерах контактных окон (5 ͯ 5) мкм². Существуют модификации топологии данного ЗЭ, где можно установить разделительную диффузию между словами и двухслойную металлизацию. Например, на рис. 10 дан вариант топологии, где совмещены функции выборки и считывания (при этом несколько увеличивается площадь, занимаемая ЗЭ). В другой модификации шина словарной выборки совмещена с инжектором полоскового типа. Недостаток топологии: из-за влияния последовательного сопротивления инжектора неравномерно распределяется мощность между ЗЭ одного слова.

рис. 10

3. ЗЭ с двунаправленными ключами

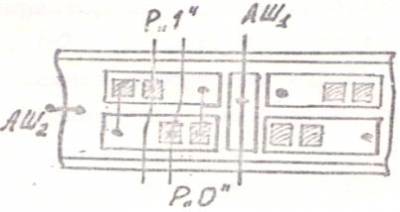

ЗЭ с двунаправленными ключами, в котором прямая инжекция неосновных носителей используется не только для питания схемы, как в обычных инжекционных ЗЭ, но и для связи триггера с шинами записи и считывания. Применение такого способа выборки сильно упрощает организацию металлизации в матрице памяти на основе этого ЗЭ. Роль токозадающих и развязывающих транзисторов выполняют совмещенные горизонтальные структуры р-п-р типа. Это обеспечивает очень низкий уровень мощности рассеиваемой в режиме хранения. На рис.16б представлено поперечное сечение интегральной структуры эле¬мента памяти, все компоненты которой расположены в одном кармане п-типа. Один элемент памяти при минимальной ширине металлизации 5мкм занимает на кристалле площадь, равную 2000мкм2[1].

Заключение

Таким образом, рассмотрены различные варианты электрических схем ЗЭ с инжекционным питанием и различные варианты топологии этих ЗЭ.

Увеличение плотности компоновки и улучшение фактора качества (1/ρt3) схем с инжекционным питанием может быть достигнуто не только путем усовершенствования электрических схем ЗЭ, но и путем применения новых достижений технологии ИС.

В первую очередь это касается методов изоляции. В ЗЭ с инжекционным питанием нет необходимости в изоляции отдельных компонентов, так как они самоизолированы, но нужно, например, изолировать эпитаксиальные полосы, служащие в качестве шин выборки. Изоляция р-п переходами не удовлетворяет разработчиков микро¬схем, т.к. р-п переходы занимают слишком большую площадь на кристалле. Наиболее перспективными, по-видимому, являются комбинированные методы изоляции диэлектриками р-п переходами. В частности можно использовать метод "Изопланар" (фирма Foirchaild), где изоляция в боковых направлениях осуществляется областями SiO2, а скрытый п+-слой образует с р-подложкой обратно смещенный р-п переход. Боковая изоляция может осуществляться с помощью вытравленных в кристалле V–образных канавок (метод ИВК, фирма Raytheon), либо с помощью канавок вытравленных, а затем заполненных поликристаллическим кремнием (метод ИЗК, фирма Motorola).

Необходимо также отметить, что ЗЭ с инжекционным питанием необходимо формировать в тонких=(1÷3)мкм низкоомных эпитаксиальных пленках с "скрытым" п+ слоем . При использовании "скрытых" п+-слоев возрастает инверсный коэффициент усиления

п-р-п транзисторов, увеличивается коэффициент передачи токозадающих р-п-р транзисторов. Функциональную плотность ЗУ можно увеличить, решив проблему многослойной металлизации, т.к. при этом упрощается топология ЗЭ и разводка металлизированных межсоединений и, следовательно, более экономично используется площадь кристалла.

Применение новых технологических методов позволит разместить один элемент памяти на площади 700мкм² или биполярное ЗУ емкостью 16Кбит на кристалле размерами 4,5x4,5мм2.

Как указывалось выше, схемы с инжекционным питанием обладают высокой функциональной плотностью и пониженной потребляемой мощностью. Поэтому представляется интересной возможность использовать в качестве обслуживающих схем – схемы на основе ИЛ. В частности, сравнение дешифраторов на три входа реализованных на базе ТТЛ или ДТЛ схем и ИЛ показывает, что такой дешифратор на базе ИЛ занимает более чем в три раза меньшую площадь на кристалле [3].

Источники информации

1. Лапшинский В.А. Диплом, 1975. - Основной источник информации.

2. www.wikipedia.org - Основные определения.

3. www.valinfo.ru – Информация по оформлению отчета.

Источник: http://Лапшинский В.А. Диплом, 1975. |