| Статистика |

Онлайн всего: 1 Гостей: 1 Пользователей: 0 |

|

СТРУКТУРНО-ЛОГИЧЕСКИЕ СРЕДСТВА РЕАЛИЗАЦИИ КВАЗИСТАТИЧЕСКИХ СБИС ПАМЯТИ

Научно-исследовательский ядерный университет

Московский инженерно-физический институт

Факультет «Автоматики и электроники»

Кафедра «Микро- и наноэлектроники»

Курс «Компьютерный практикум»

СТРУКТУРНО-ЛОГИЧЕСКИЕ СРЕДСТВА РЕАЛИЗАЦИИ

КВАЗИСТАТИЧЕСКИХ СБИС ПАМЯТИ

Преподаватель: доцент В. А. Лапшинский

Подготовила студентка А4-09 Храмцова Д.С.

Москва 2013

Оглавление

Аннотация………………………………………………………………………………..4

Глоссарий…………………………………………………………………………………5

Введение………………………………………………………………………………….6

Способы регенерации и варианты квазистатических

структур……………………………………………………………………………………7

Морфологический анализ квазистатических структур

памяти……………………………………………………………………………………….9

Обобщенные показатели качества и особенности

применения квазистатических структур………………………………13

Заключение…………………………………………………………………………….14

Список литературы…………………………………………………………………16

Аннотация

Данная работа посвящена статье А. Г. Алексеенко, В. А. Лапшинского, Е. М. Онищенко «СТРУКТУРНО-ЛОГИЧЕСКИЕ СРЕДСТВА РЕАЛИЗАЦИИ КВАЗИСТАТИЧЕСКИХ СБИС ПАМЯТИ». В данной статье проводится анализ квазистатических структур, реализующих различные способы адресной регенерации (синхронной, асинхронной, распределенной, сосредоточенной и т. д.). Предлагаются обобщенные показатели и выполняются численные оценки этих показателей, а также избыточности некоторых вариантов организации квазистатических СБИС памяти по сравнению с типовыми статистическими и динамическими микросхемами.

ГЛОССАРИЙ

Регенерация памяти - обновление памяти через определённые промежутки времени во избежание потерь данных. Он реализуется специальным контроллером, установленным на материнской плате или же на кристалле центрального процессора. На протяжении времени, называемого шагом регенерации.

Квазистатическая память – память, в которой регенерация полностью контролируется внутренней логикой микросхемы и не требует никаких внешних сигналов.

Информационная емкость , информационный объем (information capacity) - способность запоминающего устройства разместить определенное количество информации. Измеряется максимальным количеством единиц данных (битов, байт, и т. д.), которое может храниться в запоминающем устройстве.

ВВЕДЕНИЕ

Специфической особенностью СБИС памяти на основе динамических элементов памяти (ЭП) является необходимость восстановления информации как в каждом цикле обращения, так и периодически в ЭП, к которым длительное время обращение не производилось [1-2]. Традиционным решением данной проблемы считается использование аппаратных средств в виде специальных устройств управления регенерацией, проектируемых на основе микросхем малой и средней степени интеграции либо БИС контролеров[1-2]. Применяется также программный способ.

В последнее время появились сообщения о разработке за рубежом серийных СБИС ОЗУ емкостью 16-64 Кбит на основе динамических ЭП и встроенных на кристалл схем управления регенерацией [1-2]. В подобных СБИС помять функция восстановления информации переносится на кристалл, что является одним из примеров реализации принципа автономной организации хранения в процессорно - ориентированных структурах памяти. Предлагается отнести СБИС памяти с дополнительной функциональной возможностью саморегенерации к классу квазистатических, как и структуры, содержащие динамические ЭП и нуждающиеся в энергии «подкачки» от внутреннего или внешнего источника.

Цель данной работы – сравнительный анализ структурно-логических вариантов организации квазистатических СБИС памяти с саморегенирацией и особенности их применения.

СПОСОБЫ РЕГЕНИРАЦИИ И ВАРИАНТЫ КВАЗИСТАТИЧЕСКИХ СТРУКТУР

Наиболее распространенный способ регенерации, используемый в современный СБИС ОЗУ , - последовательная адресация строк ЭП или перебор адресов регенерации (АР) R. Регенерация при этом осуществляется синхронным или асинхронным способом.

Синхронная генерация может быть как сосредоточенной в каком-либо интервале времени, так и равномерно распределенной по всему периоду. Основные достоинства сосредоточенного способа: возможность работы процессора с предельной скоростью, минимальное число переключений источников питания, что снижает уровень помех ОЗУ; минимальное потребление мощности в аварийных ситуациях; возможность тренировки ЭП при первоначальном подключении к источнику питания. Для распределенной регенерации характерны возможность проведения прозрачной регенерации и равномерное распределение мощности, потребляемой СБИС. Достоинством синхронного способа является строго фиксированное время выборки и длительностей циклов выборки и регенерации, а недостатки – потеря информации при отсутствии тактовых импульсов (ТИ) и затраты на паузы между тактовыми сигналами, если ТИ подаются непрерывно. Для выполнения синхронной регенерации в корпусе квазистатической СБИС памяти предусматривается управляющий вывод ТИ (рис. 1).

Асинхронная регенерация позволяет сократить непроизвольные паузы, но приводит к затягиванию циклов при наложении во времени запросов на выборку кристалла (ВК) и регенерацию (ЗР). Асинхронный способ регенерации упрощает согласование ОЗУ с процессорами различной производительности.

Разрабатываются новые способы регенерации: современная и разреженная. Современная реализуется путем сравнения текущих адресов выборки и АР. Разреженная регенерация основывается на том, что любое обращение к СБИС ОЗУ сопровождается регенерацией по адресу обращения.

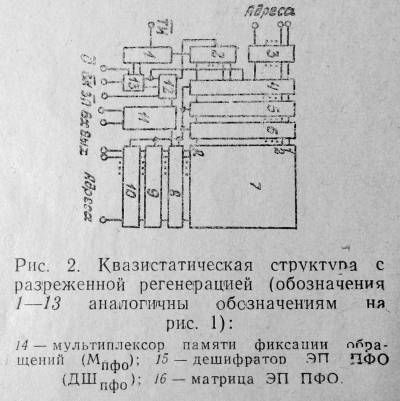

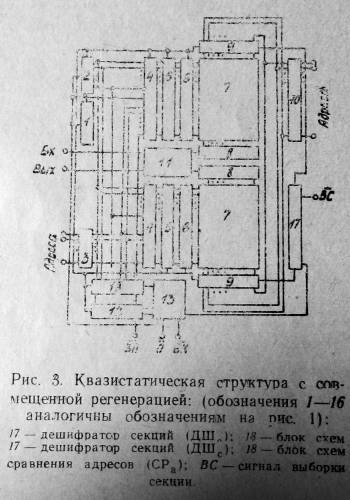

Для построении квазистатических структур с синхронной регенерацией в типовую структуру динамической СБИС ОЗУ необходимо ввести ряд дополнительных блоов управления (БУ): таймер для задания периода регенерации и счетчик 〖СЧ〗_а либо регистр (рис.1). Блоки 〖СЧаи Ра могут подсоединяться к накопителю через мультиплексор адресов либо адресных формирований (АФ).

При реализации квазистатических структур с асинхронной регенерацией помимо БУ необходимо ввести арбитр асинхронных обращений для надежного и быстрого разрешения конфликтных ситуаций ВК и ЗР. Для выполнения разреженной регенерации требуется следующие дополнительные БУ: блок ЭП для памяти фиксации обращений и блоки схем уравнения к этим ЭП. При совмещении циклов выборки и регенерации необходимо разбить накопитель на секции с соответствующими адресными и разрядными БУ и использовать блок схем сравнения адресов . Структуры СБИС памяти, реализующие данные способы регенерации, представлены на рис. 2,3 .

МОРФОЛОГИЧЕСКИЙ АНАЛИЗ КВАЗИСТАТИЧЕСКИХ СТРУКТУР ПАМЯТИ

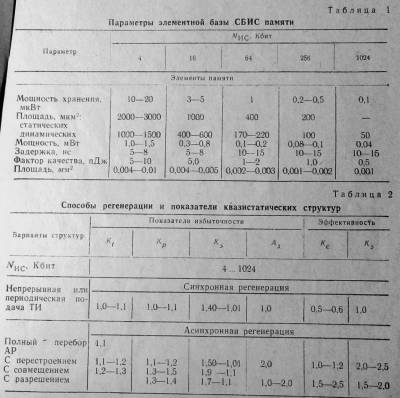

Основные характеристики СБИС памяти – информационная емкость N(СБИС@), быстродействие, потребляемая мощность, площадь кристалла и количество дополнительных выводов Ав корпусе ИС. В качестве критериев эффективности предлагается использовать показатели избыточности квазистатических структур по сравнению с аналогичными типовыми статическими и динамическими СБИС ОЗУ.

В соответствии с методикой и ориентировочными параметрами элементной базы (табл.2) проведены оценки показателей избыточности некоторых квазистатических структур (табл.2). При этом необходимо сделать следующие замечания.

Быстродействие структур определяется в соответствии с табл. 3. Предполагается, что длительность цикла записи информации (t(ц.в.))max≤t(ц.в.) Для асинхронных структур при наложении сигналов ВК и ЗР возможно увеличение времени выборки до (t(ц.в.))max≈t(ц.в.)+t(ц.р.) (распределенная регенерация) или до (t(ц.в.))max≈t(ц.в.)+Rt(ц.р.)(сосредоточенная регенерация). Временная избыточность асинхронных структур уменьшается при использовании арбитров обращений с повышенным быстродействием. Минимальные потери времени на регенерацию Tз могут быть достигнуты в структурах с разреженной и совмещенной регенерацией, где время занятости может приближаться к нулю (табл. 3) .

устройст Здесь tвк,t(Ба ),t(Бр ),t(ДШа ),t(ДШр ),tАФ,tРФП,tН,tВВ- задержки блоков ВК, Ба,Бр, РФП, Н, ВВ соответственно; tвоаст^',tвосст^''- длительности восстановления исходных состояний блоков ВВ и потенциалов управляющих ЭП шин; (tсч)min- минимальная длительность считываемого сигнала, определяемая внешними вами; tp- длительность регенерации в динамическом ЭП. t(Ma )- задержка переключения Ма; ξ=2-4- коэффициент, характеризующий мультиплексированный ввод адреса; ta,t(Ca ),t(Ca )- задержки блоков А и С соответственно: fв,fр- частоты поступления запросов на выборку и регенерацию; pc^R,pc^t- вероятности совпадения кодов адреса выборки и АР и моментов поступления сигналов ВК и ЗР соответственно. «д», «к» - индексы показателей динамических и квазистатических структур.

Потребляемая мощность. Данные, приведенный в [1], показывают, что практически независимо от организации и информационной емкости СБИС справедливо (Рв^т)ст=0,5-1,0 Вт/корпус и (Рв^т)дин=0,2-0,6 Вт/коппус. Эти значения, очевидно, связаны с удовлетворением ограничения на предельно-допустимую мощность, рассеиваемую корпусом ( Р≤0,5÷1,0 Вт/корпус), и стремлением получить максимальное быстродействие. Поэтому квазистатические СБИС памяти следует проектировать также с учетом Р_д. Блоки можно проектировать на основе вентилей с минимальной потребляемой мощностью.

Информационная емкость и степень интеграции функций. Из табл.2 следует, что на современном уровне развития технологий при емкости СБИС ОЗУ, равной 4-64 Кбит, избыточность квазистатических структур в зависимости от использованного способа регенерации составляет 10-40% и существенно уменьшается по мере совершенствования технологии и увеличения емкости СБИС до 256-1024 Кбит и более.

ОБОБЩЕННЫЕ ПОКАЗАТЕЛИ КАЧЕСТВА И ОСОБЕННОСТИ ПРИМЕНЕНИЯ КВАЗИСТАТИЧЕСКИХ СТРУКТУР

Для обобщенной оценки вариантов структур СБИС памяти разных типов предлагается использовать показатель приведенной энергии переключения Э и пропускную способность С:

Э= (t(ц.в) Pв)/NСБИС 1/(1-Тз⁄Тр ); С= 1⁄t ̃(ц.в) =N_max⁄T_p .

Показатель Э позволяет учитывать потери мощности и времени на регенерацию. При этом известный показатель добротности Д при t(ц.в)≈tв и Тз=0 для статических СБИС является частным по отношению к предложенному Э= 1/Д.

Показатель С позволяет дать не только дифференциальную оценку быстродействия структуры в отдельном цикле выборки, но и получить интегральную оценку скорости передачи информации с учетом потерь времени на регенерацию.

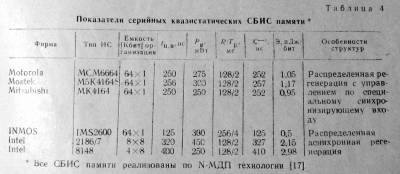

Обобщенные критерии эффективности Кэ=Э^т⁄Эj ; (Эj^т)⁄Эsj и Кc=Cj⁄C^T , где j – индекс варианта структуры. Численные оценки эффективности гипотетических квазистатических СБИС памяти (табл.2) и известных серийных микросхем (табл.4) показывают, что при одинаковой степени интеграции и технологических допусках эти структуры по показателям Э и С превосходят типовые статические и динамические в 1,2-2,5 раза. ВБ аварийных ситуациях для предотвращения потери информации требуется подача специальных сигналов управления регенерацией ТИ.

Следует отметить, что наиболее удобны в применении квазистатические СБИС памяти, допускающие перестраиваемое синхронно-асинхронное функционирование.

ЗАКЛЮЧЕНИЕ

В настоящее время одним из перспективных принципов проектирования СБИС памяти – принцип автономной организации хранения. В частности, квазистатические СБИС ОЗУ по обобщенным показателям в 1,2-2,5 раза превосходят типовые статистические и динамические СБИС. Их дальнейшее совершенствование возможно при создании энергонезависимых СБИС ОЗУ.

Аппаратурная избыточность квазистатических структур не превышает 5-30% общей площади кристалла; незначителен также вклад дополнительных схем управления регенерацией в потребляемую мощность; незначительно уступая СБИС памяти по быстродействию(не более чем в 1,5 - 2 раза), квазистатические микросхемы значительно превосходят последние по информационной емкости при одинаковой степени интеграции кристаллов и обладают пониженным потреблением мощности в режиме хранения информации; на современном уровне развития технологии при емкости 4 – 64 Кбит целесообразно создать квазистатические структуры с простейшими способами регенерации. Данный вывод подтверждается разработкой многими зарубежными фирмами серийных квазистатических СБИС (см. табл. 4). С развитием технологии и переходом к СБИС памяти емкостью 256 Кбит – 1 Мбит и более целесообразно реализовать микросхемы с совмещенной и разреженной регенерацией и перестраиваемой структурой.

Проведенный анализ показывает, что минимальные потери времени на регенерацию обеспечивают квазистатические структуры с асинхронной распределенной регенерацией. Следует отметить, что введение дополнительных схем управления в квазистатических СБИС ОЗУ упрощает реализацию комбинированных последовательно-параллельных способов выборки и построение процессорно - ориентированных структур. Эффективность квазистатических СБИС памяти, процент выхода годных и надежность повышаются при использовании методов резервирования элементов памяти [2].

СПИСОК ЛИТЕРАТУРЫ

А.Г. Алексеенко, В.А. Лапшинский, Е.М. Онищенко. Структурно-логические средства реализации квазистатических СБИС памяти. – Электронная техника, серия 3, Микроэлектроника, 1983, №3, с. 55 - 63.

Алексенко А. Г., Лапшинский В. А. Современное состояние, особенности проектирования и перспективы развития сверхбольших ИС памяти. – Зарубежная радиоэлектроника, 1979, № 12, с. 15 - 45. |

| Категория: Конспекты (курсы КП и ПК) | Добавил: Darya (29.05.2013)

| Автор: Храмцова Д.С.

|

| Просмотров: 916

| Рейтинг: 0.0/0 |

Добавлять комментарии могут только зарегистрированные пользователи. [ Регистрация | Вход ] |

|