| Статистика |

Онлайн всего: 1 Гостей: 1 Пользователей: 0 |

|

Коммутационная матрица в сетевом оборудовании

Оглавление

Введение…………………………………………………………………………………..4

Системы и методы коммутации…………………………………………..4

Архитектура с разделяемой шиной……………………………………….5

Архитектура с разделяемой памятью………………………………….5

Архитектура crossbar……………………………………………………………. 6

Многоступенчатая система коммутации…………………………….6

Архитектура коммутационной матрицы…………………………….7

Производительность…………………………………………………………….12

Требования к коммутационной матрице……………………………….13

Заключение…………………………………………………………………………….14

Литература…………………………………………………………………………..14

Приложение…………………………………………………………………………..14

ВВЕДЕНИЕ

Необходимость передавать данные на высокой скорости с минимальной задержкой привела к появлению сверхбыстрых коммутационных структур, способных переключать миллионы пакетов или терабайтов информации в секунду. Коммутационные матрицы играют решающую роль в таком сетевом оборудовании, как маршрутизаторы и коммутаторы поскольку они определяют общие характеристики системы, например, производительность, скорость, стоимость и срок службы. Таким образом, они, несомненно являются самым сердцем сетей. Коммутационные матрицы подходят для сетевого оборудования. У коммутирующей матрицы две основные функции: обеспечивать связь для передачи данных между входными и выходными портами и обеспечивать соблюдение любых требований к качеству обслуживания(QoS). На рынке существует большое количество коммутационных архитектур, предлагающих широкий выбор для индустрии.

Существует большое число различных высокоскоростных коммутационных архитектур, основанных на многочисленных маршрутизаторах и системах коммутации(оптических и электронных), которые существуют сегодня на рынке, часто с довольно отличительными характеристиками. На коммутационные матрицы влияют следующие факторы(вследствие чего они широко дифференцированы): режим(и конфигурация) взаимосвязи между входящими и выходящими портами), расположение, объем буферизации памяти, внутренняя пропускная способность, разрешение конфликтов доступа к ресурсу, производительность, масштабируемость, сложность проектирования и реализации, отказоустойчивость, функциональность управления и контроля. Далее будет рассказано о наиболее применяемых архитектурах и их методах коммутации.

СИСТЕМЫ И МЕТОДЫ КОММУТАЦИИ

Коммутационная матрица размера N × N имеет N входов и N выходов, причем входной и выходной порт используют одну и ту же связь, поэтому скорости входной и выходной линии предполагаются одинаковыми. Существуют коммутационные архитектуры основанные на пакетах(переключающиеся пакеты переменного размера) или основанные на ячейках(переключающиеся пакеты фиксированного пакета, называемые ячейками). Фотонная коммутация пакетов использует аналогичную архитектуру как и электронная коммутация пакетов, обеспечивая функциональность, аналогичную коммутации

каналов(полупостоянные соединения) на таких скоростях, как 10 Гбит/с и выше [1].

Ячеистая архитектура работает в полностью синхронном режиме и может предоставить определенные преимущества в проблемах с эксплуатацией и производительностью: определенная задержка, оптимизированное использование буфера и меньшая сложность. На основе режима соединения на сегодняшний день было предложено несколько различных архитектур и систем коммутации. Существуют следующие основные типы коммутационных матриц в зависимости от режима соединения между входным и выходным портами коммутатора.

АРХИТЕКТУРА С РАЗДЕЛЯЕМОЙ ШИНОЙ(Shared Bus)

Данная архитектура в качестве разделяемой среды использует шину, обеспечивающую связь связь подключенных к ней портов(устройств ввода-вывода). В каждый момент времени только одному устройству разрешено передавать по ней данные. Чтобы система была неблокирующей, необходимо чтобы сумма скоростей портов матрицы была меньше скорости шины, что значит, что производительность всей системы ограничена производительностью шины. Общая структура показана на рис.1 [2].

Рис. 1. Архитектура с разделяемой шиной

АРХИТЕКТУРА С РАЗДЕЛЯЕМОЙ ПАМЯТЬЮ(Shared Memory)

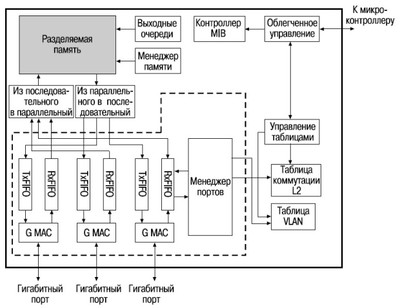

Улучшение архитектуры с разделяемой шиной привели к появлению архитектуры с разделяемой шиной. Данная архитектура обычно реализуется с помощью использования быстрой памяти RAM в качестве буфера коммутационной системы, необходимого для хранения входящих пакетов перед их передачей. Для обеспечения неблокирующей работы полоса пропускания памяти для операции должна быть равной максимальной суммарной полосе пропускания всех входящих портов. Архитектура ограничена скоростью доступа к памяти, следовательно плохо масштабируема.

Входящие пакеты преобразуются из последовательного формата в параллельный и затем записываются в двухпортовую память. В каждый момент времени только один порт может поместить кадр в ячейку разделения памяти, заголовки каждого кадра передаются в контроллер памяти и уже он определяет выходной порт и выходную очередь. Затем кадры отправляются на соответствующие выходные порты, где они преобразуются из параллельного формата в последовательный. Типовая архитектура коммутаторов с разделяемой памятью приведена на рис.2.

Рис.2 Архитектура с разделяемой памятью

АРХИТЕКТУРА НА ОСНОВЕ КОММУТАЦИОННОЙ МАТРИЦЫ(Crossbar.)

Данная архитектура характеризуется наличием безбуферных коммутирующих элементов и арбитра, который управляет передачей трафика между входами и выходами матрицы. Отсутствие буферов компенсируется наличием буферов у входных и выходных портов. Обычно используется три метода буфферизации(входные и выходные буфферы и комбинированные входные и выходные буферы)

В архитектурах на основе crossbar переключение выполняется матричным способом между входами и выходами. Crossbar коммутаторы довольно популярны для использования в маршрутизаторах и коммутаторах из-за простоты конструкции, экономической эффективности и определенных функций масштабируемости. [3]

МНОГОСТУПЕНЧАТАЯ СИСТЕМА КОММУТАЦИИ (Multistage Interconnection Networks)

Многоступенчатые структуры представляют собой модульные архитектуры, построенные из более мелких компонентов коммутации. Эти большие структуры могут поддерживать большую емкость, благодаря чему эффективно разрешают проблему масштабируемости (например, преодоление ограничений порта и емкости).

Что касается места хранения пакетов в коммутаторе, буферы памяти могут быть расположены на входной стороне (входная очередь), выходной стороне (выходная очередь), внутри самой коммутационной матрицы (центральная очередь; например, одна общая память для всех входных и выходных портов) или их комбинации. Архитектуры, которые реализуют входную очередь, страдают от феномена блокировки, известного как начальный уровень (HOL/head-of-line). Блокировка HOL происходит тогда, когда более одного пакета пытаются получить доступ к одному и тому же выходу.

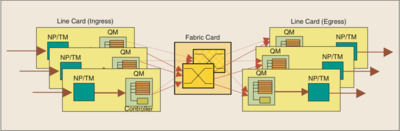

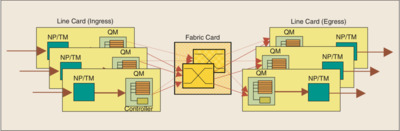

Коммутационная матрица и любые связанные с ней буферы могут быть размещены как на одной плате, так и нет. Конфигурация большой системы коммутации может включать в себя очереди (например, администратор очередей [QM-queue manager)] вместе с любыми компонентами для обработки пакетов, таких как сетевой процессор (NP-network processor) и / или диспетчер трафика (TM-traffic manager), размещенные на линейной плате, в то время как сам коммутационный элемент расположен на отдельной матричной плате, как показано на рисунке 3. Такая конфигурация является типичной для маршрутизаторов и коммутаторов. В матричную плату также может входить дополнительная буферизация в зависимости от реализованной архитектуры. Линейные и матричные карты могут быть соединены через высокоскоростную объединительную плату. Коммутационная матрица сочетается с пакетными интерфейсами (буферами) и любыми возможностями обработки и управления, такими как маршрутизация, управление синхронизацией, образуют узел маршрутизации (коммутации) в сети с коммутацией пакетов.

Рис.3 Общая схема коммутирующей системы

АРХИТЕКТУРА КОММУТАЦИОННОЙ МАТРИЦЫ

Коммутационные матрицы могут быть одноступенчатыми, где пакеты переключаются между входами и выходами матрицы за один шаг, или многоступенчатыми, построенные путем каскадирования нескольких одноступенчатых переключающих модулей, называемых «коммутирующие элементами» (SEs-switching elements). Многоступенчатые переключатели являются архитектурными модулями с пространственным разделением, то есть переключение выполняется путем соединения входа с выходной линией. Многоступенчатые структуры (MINs-Multistage interconnection networks) представляют собой большой и особый класс коммутаторов пакетов. Они широко используются в различных других областях, таких как телефонные сети и мультипроцессорные системы, то есть для соединения процессоров с модулями памяти. Многоступенчатые сети быстро и легко масштабируются, поскольку они построены по модульному принципу, так как реализованы с использованием меньших SE и предлагают гораздо меньшую сложность, чем просто crossbar.

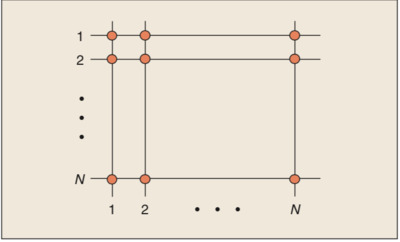

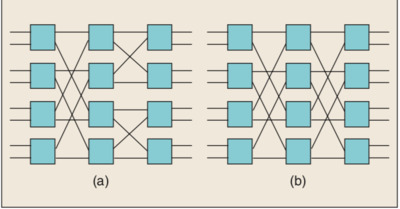

Самая простая форма (с точки зрения проектирования) соединительной сети - это crossbar. Crossbar основан на одноступенчатой сети точек пересечения, образующих полностью взаимосвязанную сетку или коммутационную матрицу, как показано на рисунке 4. Точки пересечения реализуются с использованием полупроводниковых коммутаторов, которые активируют путь между входом и выходом порт. Очевидно, что, поскольку число точек пересечения растет с увеличением площади порта коммутатора, архитектура crossbar имеет определенные ограничения. Структура crossbar, которая содержит в себя буфер в каждой точке пересечения для того, чтобы справиться с потенциальной внутренней блокировкой, называется буферизованной.

Рис.4. Crossbar

SE, которые составляют основной функциональный блок для сети передачи, обычно имеют небольшой размер порта (например, 2 x 2) и способны переключать пакеты автономно (без централизованного управления) и независимо. Если SE не имеют возможности буферизации, тогда мы обращаемся к небуферизованной коммутации. Сеть N x N, построенная из d x d элементов, будет состоять из минимум n = logd N ступеней. На рисунке 5 показаны примеры многоступенчатых коммутационных матриц, основанных на трехступенчатых сетях присоединения (N = 8), которые построены из 2 x 2 SE. Многоступенчатый коммутатор может быть естественным образом увеличен (по количеству портов), если мы рассмотрим дополнительные этапы. [4]

Рис.5. Многоступенчатые коммутирующие структуры: (а) Banyan и (b) Omega

В зависимости от того, как связаны SE на всех этапах сети соединений, могут быть созданы различные типы (топологии) многоступенчатых сетей, как показано на рисунке 5 (a) и (b), где структуры Banyan и Omega показаны соответственно. Если существует только единственный путь между входом и выходом, пакеты могут самостоятельно маршрутизироваться по непересекающимся путям, которые устанавливаются до переключения пакетов, представленных в сети. Однако структуры типа Banyan (такие, как изображенные на рисунке 5) могут пострадать из-за внутренней перегрузки (то есть возникает конфликт, когда два отдельных пакета запрашивают доступ к одной и той же ссылке). [5]

Матрица может быть построена таким образом, чтобы для любой пары вход-выход существовало несколько путей, что решает проблему внутренней перегрузки. Сеть типа Banyan может легко стать сетью с многоступенчатым распространением, если ее увеличить, добавив m дополнительных ступеней, где m ≤ n - 1. Расширенная сеть Banyan, известная как сеть Benes, показана на рисунке 6 (a). Сеть Benes имеет 2log2 N – 1 этапов, где каждый этап содержит N / 2 (2 × 2) SE.

Другим способом многоступенчатого распространения является добавление коммутатора Clos, представляющий собой трехступенчатую структуру. Коммутатор Clos, может быть построен из коммутаторов k (m × r) в первой и третьей ступени и из коммутаторов r(k × k) в средней ступени, с N = mk. [6]

Интересной многоступенчатой архитектурой является коммутатор Spanke-Benes, который рассматривается как компромисс между crossbar и Benes коммутатром. Коммутатор Спанке-Бенеса N × N требует N ступеней и может быть реализован с помощью N (N - 1) / 2 SE (2 × 2). В этом типе не все пути имеют одинаковую длину, и путь может пересекаться между N / 2 и N SE.

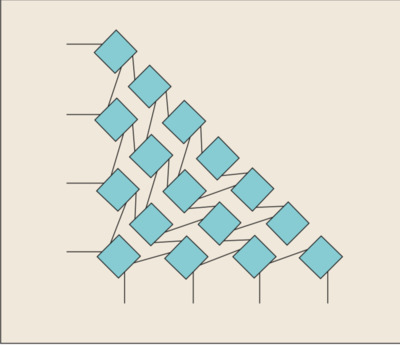

На рис. 6 представлена многоступенчатая реализация crossbar архитектуры, в которой 4 × 4 построен с использованием 2 × 2 SE. В общем случае многоступенчатая crossbar N × N может быть реализована с N 2 SE, по 2 × 2 каждый. Отметим, что коммутатор этого типа может предоставлять несколько путей для определенных соединений ввода-вывода, в то время как длина пути может варьироваться от 1 до 2 N - 1 SE. Такие сети на основе crossbar полезны для построения больших оптических коммутационных матриц, которые считаются масштабируемыми.

Рис.6. Crossbar коммутатор 4 × 4, реализованный с помощью 2 × 2 SEs

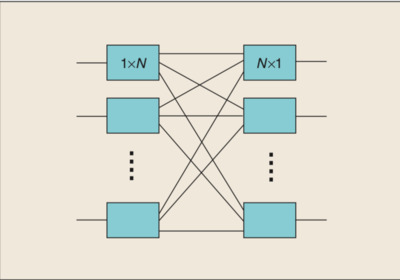

Архитектура коммутации, называемая коммутатором Spanke, которая использует N SE (каждый 1 × N), показана на рисунке 7. Хотя и не масштабируемый, коммутатор Spanke полезен для оптических коммутаторов, поскольку любые потери сводятся к минимуму из-за небольшого количества SE (только два), пересекаемых на любом пути.

Рис.7. Коммутатор Spanke

Рассмотренные нами структуры могут быть классифицированы как блокирующие или неблокирующие. Соединение блокируется, если невозможно установить соединение между произвольной парой неиспользуемых (свободных) входных и выходных портов. Так, сети типа Banyan блокируются. Некоторые многоступенчатые сети, такие как сети Clos, всегда могут предоставлять раздельные пути для передачи пакетов от входных портов коммутатора к выходным портам; таким образом, они рассматриваются как неблокирующие сети. [чтобы сеть Clos была строго неблокируемой; ссылаясь на рисунок 6 (b), он должен содержать r ≥ 2m - 1.] Crossbar характеризуются как неблокирующиеся в «широком смысле», поскольку возможна любая перестановка (схема соединения) между входами и выходами. В широком смысле архитектуры обычно предполагают подходящий механизм или элемент управления для назначения соединений.

Наконец, в некоторых сетях существующие пути соединения могут быть переставлены, если это необходимо, для удовлетворения нового запроса на соединение. Такие сети характеризуются как «регулируемые» неблокирующие; например, коммутаторы Benes и Spanke-Benes. В случае перестраиваемых сетей возможно, что реорганизация соединений неприемлема, поскольку некоторые приложения не могут быть прерваны.

Если сама коммутационная матрица работает с той же скоростью, что и входная и выходная линии коммутатора, матрица характеризуется как не имеющая ускорения (S = 1), и никакой очереди вывода не требуется. Однако, если матрица может работать на нескольких скоростях внешних каналов, она может быстрее перемещать пакеты от входов коммутатора к его выходам (S> 1). При наличии ускорения выходные очереди требуются для хранения коммутируемых пакетов. Внутреннее ускорение значительно повышает производительность коммутатора и может также компенсировать накладные расходы (обработка или другое), вносимые любыми внутренними (транспортными) протоколами.

Однако достижение очень высокого ускорения является сложным и дорогим в реализации. Ускорение до двух (S = 2) для нескольких очредей является достаточным для обеспечения производительности эквивалентно идеальной матрице коммутации с S = N. Cтоит упомянуть, что многие современные реализации коммутационных матриц используют ускорение в два.

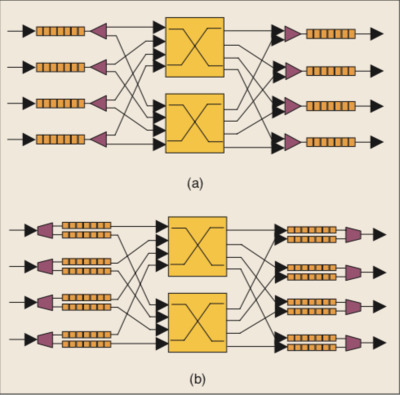

Многоплоскостные структуры, где коммутационные матрицы работают параллельно, можно рассматривать в качестве альтернативы реализации ускорения. Кроме того, многоплоскостные архитектуры коммутации способны решать проблемы масштабируемости и надежности. В зависимости от того, как входы и выходы коммутатора получают доступ, существуют различные типы многоплоскостных структур, как показано на рисунке 9. На рисунке 9 (a) единая буферная очередь (кто первым пришел, первым и вышел), в то время как на рисунке 9 (b) для каждой плоскости существует отдельная выделенная очередь. Многоплоскостные архитектуры благодаря присущему им значительному параллелизму могут обеспечить равную нагрузку (трафик распределяется по различным плоскостям коммутации).

Многоплоскостные конфигурации можно быстро и легко расширить, то есть можно добавить новую карту в случае, если система сможет поддерживать ее, таким образом, любой из них может быть легко улучшен в будущем.

Рис.9. Многоплоскостные коммутационный матрицы с буфферными очередями

ПРОБЛЕМЫ С ПРОИЗВОДИТЕЛЬНОСТЬЮ

Производительность коммутационной матрицы (общая пропускная способность, задержка, гарантии потери данных и поддержка QoS принципиально важна для системы и, следовательно, для любых приложений высокого уровня, которые она может поддерживать. Требования могут значительно отличаться; например, параметр задержки имеет решающее значение для чувствительных ко времени приложений, таких как пакетная передача голоса в реальном времени, а потеря пакетов имеет огромное значение для приложений, ориентированных на данные, таких как веб-приложения и электронная почта.

Потеря данных отрицательно влияет на общую производительность и ее нужно избегать. Потеря может быть вызвана недостаточностью или отсутствием буферного пространства (например, если используются небуферизованные SE). Не всегда имеется возможность обеспечить достаточную память, учитывая, что модули памяти дорогие. Специальные методы управления потоком, такие как метод обратного давления (сигнал, который распространяется назад, который запрещает прием дополнительных пакетов), или методы маршрутизации, такие как отклонение (выбор альтернативных путей), могут применяться для предотвращения отбрасывания пакетов, которые находятся в избытке. Производительность коммутатора можно использовать как инструмент оценки и сравнения.

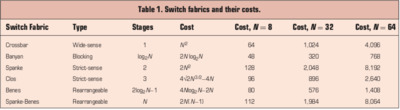

Другим важным фактором, особенно для больших коммутаторов, является сложность матрицы и, следовательно, стоимость, связанная с ее сборкой. Используя общее количество SE или ( или общее количество точек пересечения в матрице коммутации), в качестве показателя стоимости, мы можем определить стоимость C как функцию размера N коммутатора. Например, простая сеть Banyan, которая состоит из log2N этапов, где каждый этап имеет N / 2 (2 × 2) SE, имеет стоимость C = log2N × N / 2 × (2 × 2) = 2 N log2N. Стоимость или число переключений, хотя и не полностью говорят о цене, но могут использоваться в качестве величины для сравнения. Основываясь на этой функции стоимости, мы можем создать Таблицу 1, которая иллюстрирует сравнение коммутационных матриц и связанных с ними затрат для коммутаторов различных размеров N.

Отказоустойчивость (защита) - это еще один важный параметр производительности, который влияет не только на устойчивость коммутатора к сбоям, но и на работоспособность. Такой важный элемент элемент системы как коммутирующая матрица, должен быть защищен от перебоев в работе, чтобы обеспечить бесперебойный поток трафика через коммутатор. Также требуется, чтобы работа была быстро возобновлена в случае критической ситуации . Защита в коммутационных матрицах достигается и реализуется в виде резервирования - резервных матриц в конфигурации многоплоскостного коммутатора. В частности, защитные схемы коммутирования включают следующее:

1) 1: 1, где присутствуют две коммутационные матрицы, но активен только один (через нее проходит трафик), а другой находится в режиме ожидания

2) 1 + 1, где обе матрицы используются одновременно для пересылки трафика, а в случае сбоя одной другая перехватит ее трафик

3) N : 1, обобщение режима 1: 1, где присутствует более одной резервной коммутационной матрицы, и в случае сбоя главной матрицы трафик автоматически переключается на одну или сразу несколько резервных матриц.

4) N + N, N + M - присутствуют дополнительные матрицы, (например, в два и более раз больше),

ТРЕБОВАНИЯ К КОММУТАЦИОННОЙ МАТРИЦЕ

Чтобы коммутирующая матрица была востребованной на рынке, она должен обладать следующими характеристиками:

o Высокая производительность: в принципе, идеальная архитектура коммутатора должна обеспечивать стопроцентную пропускную способность независимо от применяемой схемы движения трафика, защита от любых внешних или внутренних блокировок, так как она может серьезно ухудшить производительность матрицы; минимальная задержка (менее нескольких микросекунд); работать без потери данных (при нормальных условиях движения трафика). Поддержка QoS (способность обрабатывать данные в соответствии с требованиями к трафику).

o Масштабируемость: архитектура должна быть способна масштабироватсяь и расширяться не только с точки зрения количества портов, но и с точки зрения скорости (таким образом, совокупную емкость, которая может повлиять на внутреннюю структуру коммутационной матрицы).

o Защита: соответствующий режим резервирования выбирается в зависимости от требований системы.

o Взаимодействие: архитектура должна обеспечивать соответствие существующим стандартам, а также поддерживаться другими интерфейсами и устройствами

o Физические требования: конструкция должна иметь минимальное рассеивание мощности и минимальные размеры и помехи.

o Низкая стоимость: Учитывая изобилие матриц на рынке, стоимость имеет не последнее значение. Она определяется такими параметрами как, компоненты памяти, резервирование, возможности обработки, интерфейсы и сложность системы.

ЗАКЛЮЧЕНИЕ

Основная функция коммутирующей матрицы состоит в том, чтобы эффективно и быстро передавать данные со своих входов на свои выходы согласно QoS и при этом достигать наилучшей возможной производительности. Производительность матрицы определяется ее характеристиками и конструктивными параметрами.

Коммутационные матрицы на Clos были довольно популярны в области больших, модульных коммутирующих конструкций. Матрицы на Banyan также широко используются в основном из-за их свойств самостоятельной маршрутизации применением методов для устранения любых ситуаций блокировки. Crossbar архитектуры, благодаря их экономической эффективности, также являются идеальным выбором для многих маршрутизаторов и коммутаторов, которым требуется всего несколько портов.

Мы рассмотрели пул (небуферизованных) коммутационных архитектур и их варианты реализаци, каждый из которых имеет свои достоинства и недостатки. Существуют различия между архитектурами в вопросе эффективности с точки зрения их характеристик - производительность, сложность реализации, масштабируемость и стоимость. Широкое разнообразие в выборе коммутационных матриц означает, что ни одна архитектура не является единственным идеальным вариантом. Окончательное решение в выборе архитектуры принимается в процессе проектирования в зависимости от предъявляемых требований.

ЛИТЕРАТУРА

1 https://www.sciencedirect.com/science/article/pii/S1383762105000299

2 https://www.intuit.ru/studies/courses/3591/833/lecture/14251?page=5

3 https://en.wikipedia.org/wiki/Crossbar_switch

4 Key Building Blocks for switches and Routers, Ioannis Tomkos

5 https://en.wikipedia.org/wiki/Banyan_switch

6 https://en.wikipedia.org/wiki/Clos_network |

| Категория: Рефераты (курсы КП, ПК, ИТ и Сети) | Добавил: gooseforyoursoul (19.12.2019)

| Автор: Гузь Е.А.

|

| Просмотров: 814

| Рейтинг: 0.0/0 |

Добавлять комментарии могут только зарегистрированные пользователи. [ Регистрация | Вход ] |

|