| Статистика |

Онлайн всего: 1 Гостей: 1 Пользователей: 0 |

|

Процессорно-ориентированные СБИС памяти

НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ЯДЕРНЫЙ УНИВЕРСИТЕТ "МИФИ"

Факультет Автоматики и Электроники

Кафедра Микро- и наноэлектроники

Курс «Компьютерный Практикум-13»

Домашнее задание №1

на тему

«Процессорно-ориентированные СБИС памяти»

Выполнил: Полозок Г. А. А4-09

Преподаватель: доц. Лапшинский В. А.

Москва 2013

Оглавление

Аннотация ........................................................................................4

Глоссарий.........................................................................................4

Введение..........................................................................................5

Основной текст..................................................................................6

Заключение......................................................................................10

Список литературы............................................................................10

Аннотация

В данном конспекте рассмотрены особенности структурно-логической реализации процессорно-ориентированных свербис памяти. Приведен анализ средств, обеспечивающих улучшение основных технических характеристик сверхБИС, а также расширяющих их функциональные возможности. Даются численные оценки различных параметров сверхБИС, показаны преимущества применения активно-пассивного питания.

В работе также содержатся иллюстрации в количестве 5 штук.

В работе рассматривались следующие термины: АПП, АФ, БКП, БУ, КП, МФИ, РПФ, СБИС, СТИ.

Глоссарий

АПП – активно-пассивное питание

АФ – адресный формирователь

БКП – базовый кристалл памяти

БУ – блок управления

КП – кристалл памяти

МФИ – многофункциональное использование

РПФ – разрядный формирователь-предусилитель

СБИС – сверхбольшая интегральная схема

СТИ – структурно-топологическая избыточность

Введение

В данной статье рассматриваются и систематизируются перспективные (на момент 1982 года) структурно-логические аспекты создания таких микросхем, в частности: активно-пассивная организация питания; структурно-топологическая избыточность; многофункциональное использование блоков управления; шин и выходов корпуса; организацию базовых кристаллов памяти. Несмотря на то, что статья была опубликована в 1982 году, в ней есть то, что может быть актуальным и сейчас.

Активно-пассивная организация питания

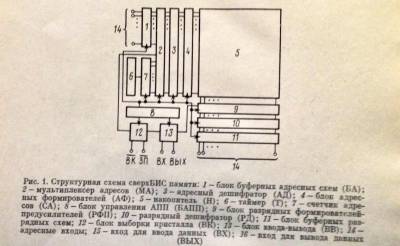

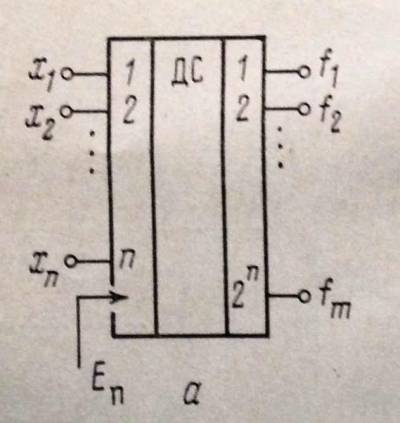

Предельная допустимая мощность (PБ) и быстродействие (tБ) БУ и микросхемы в целом ограничены. Введение дополнительных БУ для расширения функциональных возможностей СБИС памяти еще более ужесточает проблему снижения потребляемой в режиме выборки (РВ) мощности (рис. 1). Для ее решения необходима организация АПП, осуществляемая путем уменьшения тока и напряжения питания либо путем отключения элементов и БУ от шины питания или от общей шины (рис 2).

Оптимальное сочетание БУ, находящихся в активном и активно-пассивных режимах работы, определяется функцией хранения и выборки СБИС, требуемым быстродействием и допустимой мощностью, рассеиваемой корпусом микросхемы. При подключении БУ к источнику питания при организации АПП возникают дополнительные задержки, которые увеличивают время выборки СБИС (tВ) и которые могут в определенной степени быть скомпенсированы увеличением импульсной мощности.

Рис. 1 – структурная схема СБИС памяти

Оптимальное сочетание БУ, находящихся в активном и активно-пассивных режимах работы, определяется функцией хранения и выборки СБИС, требуемым быстродействием и допустимой мощностью, рассеиваемой корпусом микросхемы. При подключении БУ к источнику питания при организации АПП возникают дополнительные задержки, которые увеличивают время выборки СБИС (tВ) и которые могут в определенной степени быть скомпенсированы увеличением импульсной мощности

Одним из способов уменьшения потребляемой мощности является временное программирование блока управления АПП (см. рис. 1). Его смысл заключается в формировании импульсов питания с требуемыми задержками и минимально-допустимой длительностью.

Рис. 2 – графическое изображение дешифратора с АПП

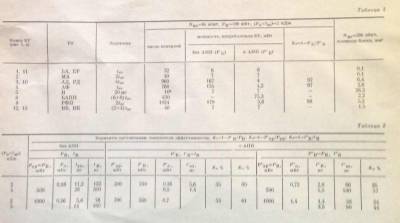

Численные оценки технических характеристик гипотетических СБИС памяти показывают, что при незначительных аппаратных затратах (~10-15%) в микросхемах с АПП достигается экономия потребляемой мощности (на 35-50%) при заданном быстродействии либо повышение быстродействия (на 25-40%) при заданном потреблении мощности (табл. 1, 2).

Таблица 1, 2

Структурно-топологическая избыточность

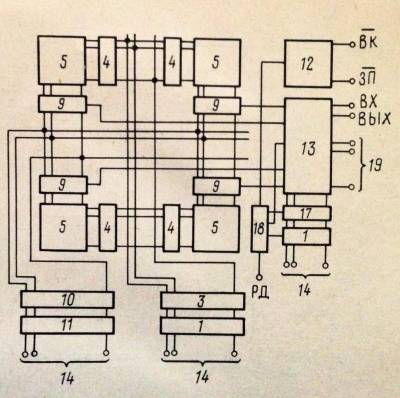

СТИ используется в СБИС памяти для уменьшения потребляемой мощности и повышения быстродей ствия и реализуется с помощью секционирования накопителя, расположения блоков АФ и РПФ между селекциями, а также при использовании дополнительных БУ, в частностиблоков АФ и РПФ. Хоть оптимальное количество ЭП, объединяемых в накопителе общими упраляющими шинами, неизвестно, анализ известных СБИС памяти показывает, что обычно объединяется 64-256 ЭП, а при емкости Nис≥4 кбит – накопитель секционируется (рис. 3).

Рис. 3 – структурная схема базового кристалла со структурно-топологической избыточностью

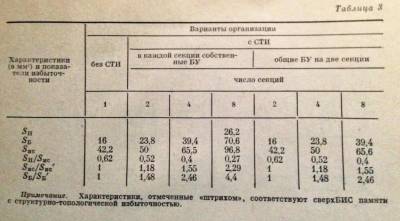

Анализ численных оценок различных вариантов секционирования накопителя (табл. 3) показывает, что с увеличением числа секций избыточность существенно возрастает. Например, при увеличении числа секций от 2 до 4 площадь кристалла СБИС памяти возрастает в 1,2-1,4 раза и более.

Таблица 3

Многофункциональное использование блоков управления, шин и выводов корпуса

МФИ является средством оптимизации избыточности кристаллов по площади, аппаратурным и энергетическим затратам. Многофункциональность определяется возможностью реализации БУ, шиной, выводом корпуса неединичного набора функций.

Целесообразно применять единый БУ для тех режимов функционирования СБИС памяти, которые связаны с последовательным перебором адресов в накопителе.

Таймер, используемый в квазистатических СБИС памяти, может быть использован для задания периода распределенной регенерации с тактовой частотой ТP/R, где ТP=2 мс – период регенерации, R – количество адресов регенерации. МФИ позволяет уменьшить площадь кристалла на 5-10% и число выводов корпуса на 30-40%.

Для реализации МФИ шин и выводов корпуса необходимо использовать технику временной коммутации, применяемую при проектировании БИС микропроцессоров.

Базовые кристаллы памяти

Реализация БКП позволяет перестраивать организацию и изменять характеристики путем подачи воздействий на выходы микросхемы в соответствии с требованиями конкретного применения, в частности, в зависимости от хода вычислительного процесса (оперативная адаптируемость). Один из вариантов имеет фиксированные металлизированные межсоединения на кристалле, а перестройка осуществляется логическим образом.

Возможности реализации БКП определяются максимальным количеством КП, размещающихся по периметру кристалла, и допустимый избыточностью СБИС памяти.

Максимальное число КП (Акп. макс) можно оценить с помощью выражения: Акп. макс=4(Lкр-hкп)/hкп, где Lкр – линейный размер кристалла, hкп – минимальный шаг размещения КП. Обычно hкп=150-200 мкм.

При незначительных дополнительных затратах площади кристалла можно расширить область применения СБИС памяти. Окончательный же вывод о перспективности различных способов организации БКП можно сделать лишь на основе комплексного анализа временной, энергетической, и аппаратурной избыточности, надежности и экономических факторов.

Заключение

В заключении можно сказать, что рассмотренные средства не только обеспечивают улучшение основных технических характеристик СБИС памяти, но и расширяют их функциональные возможности.

Применение АПП позволяет снизить потребляемую мощность при заданном быстродействии и небольших аппаратурных затратах либо повысить быстродействие при заданном потреблении мощности.

Структурно-топологическая избыточность является следствием увеличения площади кристаллов и применения управляющих шин со сложной нагрузкой. Эффективность избыточных СБИС памяти может быть повышена путем оптимальной организации кристаллов и расширения их фунцкциональных возможностей.

Прогресс технологии и увеличение максимальной площади кристаллов делают реальным реализацию базовых кристаллов памяти для создания СБИС, эффективно адаптируемых к условиям эксплуатаци.

Список литературы

1. Алексенко А. Г., Лапшинский В. А. МЭ, 1980, т. 9, № 1, с. 3.

2. Алексенко А. Г., Лапшинский В. А. МЭ, 1980, т. 9, № 2, с. 169.

3. Валиев К. А., Орликовский А. А. Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах. М.: Сов. радио, 1979.

4. Полупроводниковые запоминабщие устройства и их применение / Под ред. Гордонова А. Ю. М.: Радио и связь, 1981.

5. Алексенко А. Г., Лапшинский В. А. Зарубежная радиоэлектроника, 1979, №12, с. 16.

6. Алексенко А. Г., Онищенко Е. М. МЭ, 1874, т. 4, № 2, с.107.

7. Лапшинский В. А. МЭ, 1979, т. 8, № 4, с. 302.

8. Онищенко Е. М. В кн.: Микроэлектроника и полупроводниковые приборы / Под ред. Васенкова А. А. И Федотова Я. А. М.: Сов. радио, 1976, вып. 1, с. 123.

9. Шагурин И. И., Бушуев М. К. Электронная техника. Сер. МЭ, 1980, № 11, с. 7.

10. Кииз Р. У. ТИИЭР, 1984, т. 69, № 2, с. 152.

11. Каган Б. М., Сташин В. В. Микропроцессоры в цифровой технике. М.: Энергия, 1979.

12. Пупин А. А., Разумов Ю. И. В кн.: Проектирование и применение полупроводлниковых запоминающих устройств. М.: МИЭТ, 1978, вып. 40, с. 178 |

Категория: Конспекты (курсы КП и ПК) | Добавил: grisha1505 (02.06.2013)

| Автор: Полозок Григорий

|

| Просмотров: 638

| Рейтинг: 0.0/0 |

Добавлять комментарии могут только зарегистрированные пользователи. [ Регистрация | Вход ] |

|