НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ЯДЕРНЫЙ УНИВЕРСИТЕТ

МОСКОВСКИЙ ИНЖИНЕРНО ФИЗИЧЕСКИЙ ИНСТИТУТ (НИЯУ МИФИ)

Факультет автоматики и электроники, группа А4-11

Кафедра микро- и наноэлектроники Нанопамять  Учебный курс “Компьютерный практикум (КП)”

Преподаватель доц. Лапшинский Валерий Алексеевич

Студент Ястребов Александр Тагирович 2010 Содержание Глоссарий . . . . . . . . . . . . . . . . . . . . . . . . . 2

Список сокращений . . . . . . . . . . . . . . . . . . . . 6

Часть 1. Введние . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.1. Виды памяти . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.2. Устройство памяти . . . . . . . . . . . . . . . . . . . . . . 8

2.3. SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Часть 2. Перспективные виды памяти . . . . . . . . . . . . . . . 18

2.1. IRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.2. Trigate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.3. ZRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.4. AMD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Список использованной литературы . . . . . . . . . . . 24

Заключение . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Глоссарий

CISC (процессор со сложным набором команд) – классический дизайн подразумевающий, что процессор умеет выполнять большой набор команд (несколько сотен). Такой ассортимент инструкций по идее должен обеспечивать огромную гибкость и производительность, но только при одном условии — если набор инструкций будет использоваться эффективно. Вообще CISC-технология зарекомендовала себя неплохо: процессоры были не очень сложные, набор команд не превышал несколько сотен инструкций, а подавляющее большинство серьезных программ писали на ассемблере или частично на нем. Но время шло, и ассемблер постепенно вытеснили процедурные языки высокого уровня типа C и Pascal. А компиляторы языков программирования в силу технических особенностей не могут “творчески” использовать весь набор CISC-инструкций, они используют его шаблонно. Соответственно, большая часть команд не востребована: более 90% приложений под 80386 использовали не более 10% инструкций. Стимула выворачиваться наизнанку для оптимизации кода у программистов не было, так как каждый год росла тактовая частота процессоров, увеличивался объем оперативной памяти — все это облегчало им жизнь. В то же время набор CISC-инструкций семейства x86 продолжал хаотично расширяться, что привело к парадоксальной ситуации: инструкций стало больше, но количество программ, которые использовали бы хотя бы половину, практически не было. Но еще большие проблемы принесла CISC-технология с внедрением в процессорную архитектуру суперскалярных вычислений, при которых инструкции процессора выполняются не одним, а несколькими конвейерами. Первым суперскалярным процессором стал Pentium, содержавший два конвейера, что в теории позволяло выполнять две инструкции за такт. Однако разбиение CISC-инструкции оказалось очень сложной задачей. Альтернативной технологией стала RISC (Reduced Instruction Set Chip, процессор с сокращенным набором команд). Типичный RISC-процессор имеет очень маленький набор команд (менее сотни), причем их размер очень невелик и фиксирован (как правило — 32 бита). Они выполняются очень быстро, а любая сложная задача решается не использованием редких и “хитрых” инструкций, а их разбиением на набор маленьких команд. Какие плюсы дает такой подход? Во-первых, все инструкции выполняются одинаково быстро — за один процессорный такт. Во-вторых, разбивать код на разные конвейеры в суперскалярных процессорах становится просто. Третий плюс — более простая архитектура процессора. Вдобавок, более простая архитектура позволяет избежать ошибок в архитектуре процессора. И, наконец, разработка компиляторов под RISC-процессоры намного проще, чем под CISC. Справедливости ради стоит отметить, что классических CISC-процессоров для ПК сейчас уже не осталось: все они имеют в своей основе RISC-ядро и транслятор, который разбивает длинные CISC-команды на набор маленьких RISC-инструкций. Такова цена совместимости с предками современных PC-совместимых компьютеров. Иногда CISC-процессоры с внутренним RISC-ядром называют MISC (Mixed Instruction Set Chip, процессор со смешанным набором команд). Транзисторы – полупроводниковые устройства , управляемые электрическим током. Делятся на два типа – полевые и биполярные.

Биполярные управляются электрическим током, полевые управляются напряжением. Биполярные состоят из двух типов веществ –в одних дефицит электронов, в других избыток. Первые соединения называются полупроводниками p-типа (положительный), вторые – n-типа (отрицательный). Основной принцип работы состоит в том что на границе этих веществ образуется потенциальный барьер в несколько десятых вольта из-за разделения зарядов. Устройство начинает проводить ток, если к веществам подвести напряжение, противоположное по знаку (скажем, к р-типу – отрицательное). Транзистор состоит из эмиттера и коллектора, сделанных из вещества одного рода, к примеру n-типа, а также базы, находящейся посередине, - из p-типа. Ток поступает через эмиттер и затем переходит в коллектор.

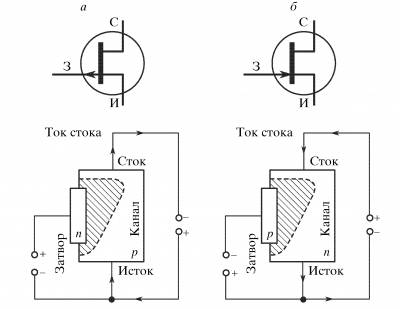

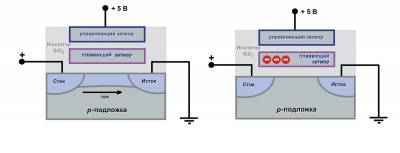

Полевые транзисторы состоят из двух типов веществ – p- и n- типа. Основу транзистора составляет полупроводник p-типа, а два электрода (эмиттер и коллектор) выполнены из n-типа. При подаче напряжения на основной полупроводник между контактами образуется мостик, передающий электроны.

Элементы полевого транзистора

Исток — электрод , из которого в канал входят основные носители заряда.

Сток — электрод, через который из канала уходят основные носители заряда.

Затвор — электрод, служащий для регулирования поперечного сечения канала.

Поскольку на затвор подан потенциал в обратном (запирающем) направлении, то основные носители тока уходят от области p-n-перехода. Основные носители от-

отталкиваются от p-n-перехода, и в основном полупроводнике — канале образуется обедненная зона, т. е. область, обедненная основными носителями. На рис. 1 она отмечена штриховкой. Если на затвор подать сигнал с обратной полярностью, то размер обедненной зоны и сопротивление канала соответственно уменьшатся, и ток в стоке возрастет. CMOS (КМОП), MOSFET (Метал-Оксид-Проводник) являются разновидностями полевых транзисторов.

Рис. 1

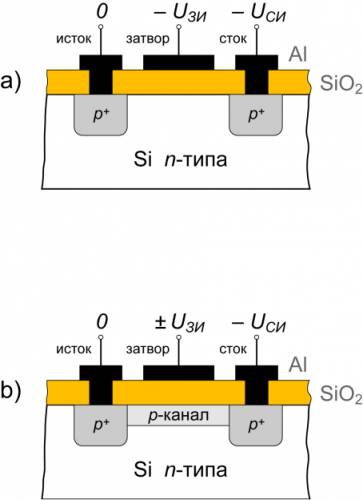

Рис. 2 Транзисторы с изолированным затвором (МДП-транзисторы)

Полевой транзистор с изолированным затвором — это полевой транзистор, затвор которого отделён в электрическом отношении от канала слоем диэлектрика (рис.2).

Затвор High-k/metal

В транзисторах CMOS tri-gate для изготовления диэлектрического слоя затвора используется материал high-k (с высоким значением k — диэлектрической постоянной) вместо традиционного диэлектрика из диоксида кремния. А электроды затвора вместо традиционного поликристаллического кремния изготавливаются из металла. Применение затвора high-k/metal позволяет снизить утечку диэлектрика затвора по сравнению со стандартным затвором из диоксида кремния/поликристаллического кремния. Использование металлических электродов устраняет истощение поликристаллического кремния и улучшает эксплуатационные характеристики транзистора. Кроме того, применение металлических электродов с работой выхода, близкой к середине ширины запрещенной энергетической зоны, позволяет снизить концентрацию примесей в подложке, что повышает подвижность транзистора, а следовательно, улучшает его общие эксплуатационные характеристики. КМОП (К-МОП; комплементарная логика на транзисторах металл-оксид-полупроводник; англ. CMOS, Complementary-symmetry/metal-oxide semiconductor) — технология построения электронных схем. В технологии КМОП используются полевые транзисторы с изолированным затвором с каналами разной проводимости. Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.) является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний). Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (N-МОП, P-МОП) является наличие как n-, так и p-канальных полевых транзисторов; как следствие, КМОП-схемы обладают более высоким быстродействием и меньшим энергопотреблением, однако при этом характеризуются более сложным технологическим процессом изготовления и меньшей плотностью упаковки Список сокращений

IEEE - Институт инженеров по электротехнике и радиоэлектронике.

Международная некоммерческая ассоциация специалистов в области техники, мировой лидер в области разработки стандартов по радиоэлектронике и электротехнике.

Эта общественная некоммерческая ассоциация профессионалов ведёт свою историю с 1884 года, объединяет более 372000 индивидуальных членов из 170 стран, в том числе более 80000 студентов. IEEE издаёт третью часть мировой технической литературы, касающейся применения радиоэлектроники, компьютеров, систем управления, электротехники, в том числе 102 реферируемых научных журнала и 36 отраслевых журналов для специалистов, проводит в год более 300 крупных конференций, принимала участие в разработке около 900 действующих стандартов.

ACM - ассоциация вычислительной техники (англ. Association for Computing Machinery, ACM) — старейшая и наиболее крупная международная организация в компьютерной области. Объединяет около 83 000 специалистов. Штаб-квартира находится в Нью-Йорке.

Ежегодно ассоциация присуждает Премию Тьюринга и премию имени Грейс Мюррей Хоппер.

Ассоциация проводит ежегодные международные студенческие соревнования по спортивному программированию.

TSMC - (аббревиатура от англ. Taiwan Semiconductor Manufacturing Company) — тайваньская компания, занимающаяся изучением и производством полупроводников. Основана в 1987 году. TSMC — крупнейший в мире производитель полупроводниковых пластин, разработавший большое количество перспективных технологий, производственных процессов, средств проектирования и стандартных архитектур.

NOR — организация ячеек флэш-памяти по принципу логической функции «ИЛИ-НЕ»: индивидуальный доступ к каждому биту и большая скорость чтения, но и большие размеры ячейки и малое быстродействие при записи.

NAND — организация ячеек по принципу логической функции «И-НЕ»: высокое быстродействие при записи и компактность, но чтение и запись информации — только блоками.

SLC (Single-Level Cell) — одноуровневая ячейка: традиционное построение флэш-памяти с возможностью хранения одного бита в одной ячейке.

MLC (Multi-Level Cell) — многоуровневая ячейка: флэш-память (как NOR, так и NAND), построенная таким образом, чтобы можно было хранить два и более бит в одной ячейке.

OneNAND — технология, разработанная Samsung, совмещает функцию высокоскоростного считывания информации NOR- и компактность NAND-flash.

LBA-NAND (Logical Block Addressing NAND) — улучшенная структура NAND-чипа компании Toshiba, позволяющая иметь единое адресное пространство независимо от объема применяемой «флэшки».

DINOR (Divided bit-line NOR) — структура NOR с разделенными разрядными линиями, Часть 1. Введение

1.1 Виды памяти

RAM (Random Access Memory) — память с произвольным доступом. В чистом виде, без приставок, сокращение RAM часто применяется для обозначения основной памяти ПК. Это любая память, содержимое которой уничтожается при выключении питания. Русское наименование «Оперативное Запоминающее Устройство» (ОЗУ) следует признать более соответствующим по смыслу, так как понятию «с произвольным доступом» соответствуют и многие типы EPROM.

DRAM (Dynamic RAM) — динамическая RAM. Это электронная память, которая требует постоянного восстановления (регенерации) своего содержимого даже при включенном питании. Русский эквивалент этого названия — динамическое ОЗУ или ЗУПВ — «Запоминающее Устройство с Произвольной Выборкой». Хотя последнее есть фактически перевод более общего термина RAM, но применяется обычно к динамической ее разновидности

SRAM (Static RAM) — статическая RAM, статическое ОЗУ. Энергозависимая память, построенная на триггерах и потому, в отличие от DRAM, регенерации не требующая. Намного более дорогая и менее емкая в расчете на микросхему.

SDRAM (Synchronous DRAM) — синхронная DRAM. Отличается наличием специального логического блока и двухбанковой структуры. Все операции записи/чтения синхронизированы с основным тактовым сигналом. Практически вся оперативная память в современных ПК относится именно к этой разновидности.

RDRAM (Rambus Direct RAM) — разновидность DRAM компании Rambus.

VRAM (Video RAM) — видеоRAM или «видеопамять»; специально разработанная для использования в видеоадаптерах разновидность DRAM с двухпортовой организацией (то есть с возможностью обращения от двух разных устройств одновременно).

WRAM (Windows RAM) — не поверите, но есть и такая! На самом деле это просто торговая марка одной из разновидностей VRAM, якобы оптимизированная для работы под Windows.

NRAM (Nano RAM) — экспериментальный тип энергонезависимой памяти на основе углеродных нанотрубок.

FRAM, FeRAM (Ferroelectric RAM) — экспериментальная энергонезависимая память на основе ферроэлектрического принципа хранения информации.

MRAM (Magnetic RAM) — экспериментальная разновидность скоростной энергонезависимой памяти на основе магниторезистивного эффекта.

NVRAM (Nonvolatile RAM) — буквально «безвольтовая», то есть энергонезависимая RAM. В принципе охватывает все разновидности EPROM и EEPROM (в том числе и Flash). NVRAM — более корректный термин, чем все остальные, так как «памятью только для чтения» ни одна из современных разновидностей ROM, строго говоря, не является. Иногда NVRAM употребляют для обозначения специальной разновидности SRAM со встроенной прямо в микросхему литиевой батарейкой (до последнего времени такие выпускались фирмой Dallas Semiconductor, ныне — подразделением Maxim).

ROM (Read-Only Memory) — память только для чтения. Русское название — «Постоянное Запоминающее Устройство» (ПЗУ) — более соответствует смыслу, так как термин относится ко всем видам энергонезависимой памяти, а не только к тем, что «для чтения» (и к перезаписываемым тоже — CD-ROM или EEPROM). В чистом виде сокращение ROM употребляется редко.

PROM (Programmable ROM) — программируемое ПЗУ (ППЗУ), обычно относят к OTPROM (One Time Programmable ROM) — «Однократно Программируемое ПЗУ». К PROM также относят и «Масочное ПЗУ» — вариант OTPROM, который программируется не самим пользователем, а на фабрике в процессе изготовления.

EPROM (Erasable Programmable ROM) — стираемая/программируемая ROM. По-русски иногда называют ПППЗУ («Перепрограммируемое ПЗУ»). Иногда употребляется как синоним UV-EPROM.

EEPROM (Electrically Erasable Programmable ROM) — электрически стираемое перепрограммируемое ПЗУ, ЭСППЗУ.

UV-EPROM (Ultra-Violet EPROM) — ультрафиолетовая EPROM, УФППЗУ. Исторически первая коммерческая разновидность EPROM, операция стирания в которой производится ультрафиолетом через специальное окошко.

Flash memory — первоначально термин придуман для обозначения прогрессивной разновидности EEPROM, в которой чтение/запись для ускорения процесса производятся сразу целыми блоками. Позднее (когда медленная EEPROM исчезла из обращения) стал фактическим синонимом EEPROM и теперь обозначает ее любые разновидности. 1.2 Устройство памяти

В 1967 году в незабвенной Bell Labs был построен первый образец EPROM — энергонезависимой памяти, которую можно было неоднократно перепрограммировать (стирая информацию рентгеном). В 1971 году (одновременно с изобретением первого микропроцессора) Intel разработала первый коммерческий образец EPROM (чип 1701 и его слегка усовершенствованный вариант 1702), который стирался ультрафиолетом через специальное окошко и потому получил название UV-EPROM.

В 1974 году в Intel под непосредственным руководством Джорджа Перлегоса (George Perlegos), будущего основателя компании Atmel, была разработана микросхема EEPROM 2816 — электрически перепрограммируемое ПЗУ. Это и был прообраз сегодняшней флэш-памяти. Основой и EPROM, и EEPROM стал транзистор с плавающим затвором, изобретенный в той же Intel Доном Фрохманом (Don Frohman). И в последующем, несмотря на смены технологических эпох, принцип устройства ячейки энергонезависимой памяти остался неизменным — какой бы способ стирания и записи информации в ней не использовался.

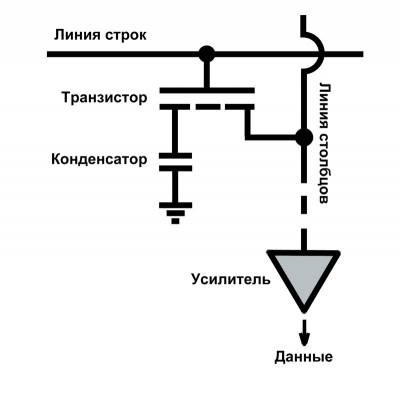

Чтобы лучше понять принцип работы EEPROM, начнем с самого простого — ячейки обычной DRAM. Как вы можете убедиться, взглянув на рис. 3, — схема состоит из одного транзистора и одного конденсатора, занимающего места раза в четыре больше транзистора (в основном вглубь кристалла). Потому ячейки DRAM довольно просто сделать очень малых размеров, а следовательно, «упаковать» их большее количество на один кристалл, не теряя в быстродействии. Отсюда и распространенность DRAM в качестве компьютерных ОЗУ — при всем кажущемся неудобстве процессов, связанных с непрерывной регенерацией содержимого.

Рис. 3 А как происходит чтение данных с такой ячейки? Для этого подается высокий уровень напряжения на линию строк (рис. 3), транзистор открывается, и заряд, хранящийся на конденсаторе данной ячейки, поступает на вход усилителя, установленного на выходе столбца. Отсутствие заряда на обкладках соответствует логическому нулю на выходе, а его наличие — логической единице.

А с чего, собственно, столь быстро утекают заряды в ячейке DRAM? Быстрая утечка зарядов обусловлена наличием транзистора, который состоит вовсе не из изолятора, а из хоть и полу-, но проводника, потому даже в запертом виде имеет мизерные, но конечные токи утечки.

Дело в том, что ввиду микроскопических размеров конденсатора (и, соответственно, емкости) в ячейке DRAM записанная информация хранится всего лишь сотые доли секунды. Несмотря на использование высококачественных диэлектриков с огромным электрическим сопротивлением, заряд, состоящий в рядовом случае всего из нескольких сотен, максимум тысяч электронов, успеет утечь так быстро, что вы и глазом моргнуть не успеете.

Решением стал сконструированный сотрудником Intel Доном Фрохманом полевой транзистор с плавающим затвором (рис 4). Если мы каким-то образом ухитримся разместить на плавающем затворе некоторое количество зарядов — свободных электронов. — то они будут экранировать действие управляющего электрода, и такой транзистор вообще перестанет проводить ток. Поскольку затвор «плавает» в толще изолятора (двуокиси кремния, SiO2), то сообщенные ему однажды заряды в покое никуда деться не могут. Далее были разработаны способы размещения электронов на изолированном от внешних воздействий плавающем затворе.

Рис. 4 Для записи на управляющий затвор подавали достаточно высокое положительное напряжение — до 36–40 В (что для микроэлектронной техники считается просто катастрофическим перенапряжением), а на сток транзистора — небольшое положительное. При этом электроны, которые двигались от истока к стоку, настолько ускорялись полем управляющего электрода, что барьер в виде изолятора между подложкой и плавающим затвором просто «перепрыгивали». Такой процесс называется еще инжекцией горячих электронов.

Для удаления электронов применялся метод квантового туннелирования. За непонятным названием кроется довольно простое (но очень сложное с физической точки зрения), по сути, явление: при достаточно тонкой пленке изолятора (10 нм) электроны, если их слегка «подтолкнуть» не слишком высоким напряжением в нужном направлении, могут «просачиваться» через барьер, не перепрыгивая его.

Превращение EEPROM во Flash происходило по трем разным направлениям. Во-первых, усовершенствовалась конструкция самой ячейки. Для начала избавились от самой противной стадии — «горячей инжекции». Вместо нее при записи стали также использовать квантовое туннелирование, как и при стирании. Потребление тока при записи снизилось на несколько порядков. Изолятор, правда, пришлось сделать еще тоньше, что обусловило довольно большие трудности с внедрением этой технологии в производство. Во-вторых, ячейку сделали несколько сложнее, пристроив к ней второй транзистор (обычный), который разделил вывод стока и считывающую шину всей микросхемы.И наконец, в-третьих, изменилась организация доступа к ячейкам на кристалле, вследствие чего этот тип памяти и заслужил наименование flash, «молния».

При такой конструкции память проигрывала в быстродействии даже жестким дискам, не то что DRAM. Давайте посмотрим, как поступили разработчики во главе с Фуджио Масуока, придумывая то, что получило название флэш-память.

Они решили, что раз потребление при записи удалось снизить, то можно записывать ячейки не индивидуально, а блоками — чем крупнее блок, тем быстрее получится. В этой схеме некий массив данных готовится заранее (помещается в специальный временный буфер SRAM — на том же кристалле, что и основная память), затем все нужные ячейки разом стираются, и одновременно же в них записывается информация из буфера. Недостатком такого метода стала необходимость перезаписи целого блока, даже если нужно изменить только один бит в одной-единственной ячейке. Но на практике это не вырастает в проблему — основные задачи, которые выполняет энергонезависимая память в современном мире, как раз и заключаются в разовой записи больших массивов (цифровые камеры, плееры и т.п.). Вот такая разновидность EEPROM и стала называться flash — за многократно выросшую скорость записи информации, ставшей сравнимой со скоростью чтения. 1.3 SRAM

История

История создания статической памяти уходит своими корнями в глубину веков. Память первых релейных компьютеров по своей природе была статической и долгое время не претерпевала практически никаких изменений (во всяком случае - концептуальных), - менялась лишь элементарная база: на смену реле пришли электронные лампы, впоследствии вытесненные сначала транзисторами, а затем TTL- и CMOS-микросхемами… но идея, лежащая в основе статической памяти, была и остается прежней…

Динамическая память, изобретенная, кстати, значительно позднее, в силу фундаментальных физических ограничений, так и не смогла сравняться со статической памятью в скорости.

В ядре

Ядро микросхемы статической оперативной памяти (SRAM - Static Random Access Memory) представляет собой совокупность триггеров - логических устройств, имеющих два устойчивых состояния, одно из которых условно соответствует логическому нулю, а другое - логической единице. Другими словами, каждый триггер хранит один бит информации, - ровно столько же, сколько и ячейка динамической памяти (см. статью "Устройство и принципы функционирования оперативной памяти. В ядре").

Между тем, триггер как минимум по двум позициям обыгрывает конденсатор: а) состояния триггера устойчивы и при наличии питания могут сохраняться бесконечно долго, в то время как конденсатор требует периодической регенерации; б) триггер, обладая мизерной инертностью, без проблем работает на частотах вплоть до нескольких ГГц, тогда как конденсаторы "сваливаются" уже на 75-100 МГц.

К недостаткам триггеров следует отнести их высокую стоимость и низкую плотность хранения информации. Если для создания ячейки динамической памяти достаточного всего одного транзистора и одного конденсатора, то ячейка статической памяти состоит как минимум из четырех, а в среднем шести - восьми транзисторов, поэтому мегабайт статической памяти оказывается по меньшей мере в несколько раз дороже.

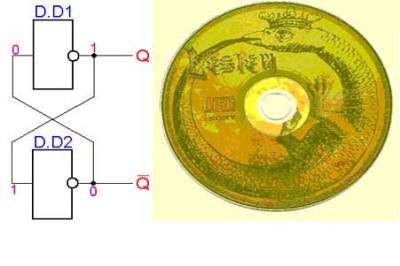

Устройство триггера

В основе всех триггеров лежит кольцо из двух логических элементов "НЕ" (инверторов), соединенных по типу "защелки" (см. рис. 5). Рассмотрим, как он работает. Если подать на линию Q сигнал, соответствующий единице, то, пройдя сквозь элемент D.D1 он обратится в ноль. Но, поступив на вход следующего элемента, - D.D2 - этот ноль вновь превратится в единицу. Поскольку, выход элемента D.D2 подключен ко входу элемента D.D1, то даже после исчезновения сигнала с линии Q, он будет поддерживать себя самостоятельно, т.е. триггер перейдет в устойчивое состояние. Образно это можно уподобить дракону, кусающему себя за хвост.

Естественно, если на линию Q подать сигнал, соответствующий логическому нулю, - все будет происходить точно так же, но наоборот!

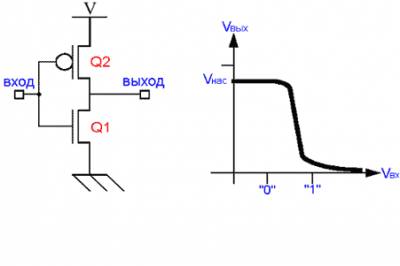

Рис. 5. Устройство простейшего триггера (слева). Образно это можно представить драконом, кусающим свой хвост Устройство элемента "НЕ" (инвертора)

Как устроен элемент "НЕ"? На этот вопрос нельзя ответить однозначно. В зависимости от имеющейся у нас элементарной базы, конечная реализация варьируется в очень широких пределах. Ниже в качестве примера приведена принципиальная схема простейшего инвертора, сконструированного из двух последовательно соединенных комплементарых /* взаимно дополняемых */ CMOS-транзисторов - p- и n- канального (см. рис. 6). Если на затворы подается нулевой уровень, то открывается только p-канал, а n-канал остается разомкнутым. В результате, на выходе мы имеем питающее напряжение (т. е. высокий уровень). Напротив, если на затворы подается высокий уровень, размыкается n-канал, а p-канал - замыкается. Выход оказывается закорочен на массу и на нем устанавливается нулевое напряжение (т. е. низкий уровень).

Рис. 6. Устройство элемента НЕ (инвертора) Устройство матрицы статической памяти

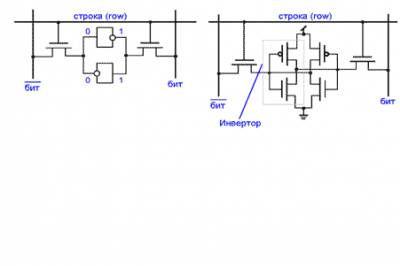

Подобно ячейкам динамической памяти (см. статью "Устройство и принципы функционирования оперативной памяти. Conventional DRAM Page Mode DRAM - "обычная" DRAM"), триггеры объединяются в единую матрицу, состоящую из строк (row) и столбцов (column), последние из которых так же называются битами (bit).

В отличии от ячейки динамической памяти, для управления которой достаточно всего одного ключевого транзистора, ячейка статической памяти управляется как минимум двумя. Это не покажется удивительным, если вспомнить, что триггер, в отличии от конденсатора, имеет раздельные входы для записи логического нуля и единицы соответственно. Таким образом, на ячейку статической памяти расходуется целых восемь транзисторов (см. рис. 7) - четыре идут, собственно, на сам триггер и еще два - на управляющие "защелки".

Рис.7. Устройство 6-транзистроной одно-портовой ячейки SRAM-памяти Причем, шесть транзисторов на ячейку - это еще не предел! Существуют и более сложные конструкции! Основной недостаток шести транзисторной ячейки заключается в том, что в каждый момент времени может обрабатываться всего лишь одна строка матрицы памяти. Параллельное чтение ячеек, расположенных в различных строках одного и того же банка невозможно, равно как невозможно и чтение одной ячейки одновременно с записью другой.

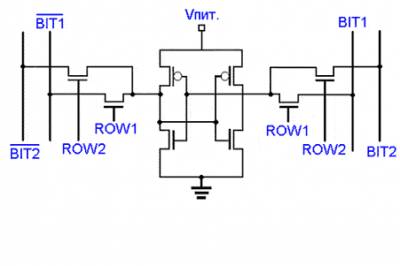

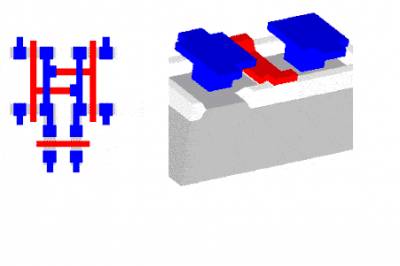

Этого ограничения лишена многопортовая память. Каждая ячейка многопортовой памяти содержит один-единственный триггер, но имеет несколько комплектов управляющих транзисторов, каждый из которых подключен к "своим" линиям ROW и BIT, благодаря чему различные ячейки матрицы могут обрабатываться независимо. Такой подход намного более прогрессивен, чем деление памяти на банки. Ведь, в последнем случае параллелизм достигается лишь при обращении к ячейкам различных банков, что не всегда выполнимо, а много портовая память допускает одновременную обработку любых ячеек, избавляя программиста от необходимости вникать в особенности ее архитектуры. (Замечание: печально, но кэш-память x86-процессор не истинно многопортовая, а состоит из восьми одно-портовых матриц, подключенных к двух портовой интерфейсной обвязке)

Наиболее часто встречается двух - портовая память, устройство ячейки которой изображено на рис. 8. (внимание! это совсем не та память которая, в частности, применяется в кэше первого уровня микропроцессоров Intel Pentium). Нетрудно подсчитать, что для создания одной ячейки двух - портовой памяти расходуется аж восемь транзисторов. Пусть емкость кэш-памяти составляет 32 Кб, тогда только на одно ядро уйдет свыше двух миллионов транзисторов!

Рис. 8. Устройство 8-транзистроной двух портовой ячейки SRAM-памяти

Рис. 9. Ячейка динамической памяти воплощенная в кристалле Устройство интерфейсной обвязки

По своему устройству, интерфейсная обвязка матрицы статической памяти, практически ничем не отличается от аналогичной ей обвязки матрицы динамической памяти (см. статью Устройство и принципы функционирования оперативной памяти. Conventional DRAM Page Mode DRAM - обычная DRAM") Поэтому, не будем подробно останавливаться на этом вопросе и рассмотрим его лишь в общих чертах.

Пожалуй, единственное различие в интерфейсах статической и динамической памяти заключается в том, что микросхемы статической памяти имея значительно меньшую емкость (а, следовательно - и меньшее количество адресных линий) и геометрически располагаясь гораздо ближе к процессору, могут позволить себе роскошь не прибегать к мультиплексированию. И потому, для достижения наивысшей производительности, номера строк и столбцов чаще всего передаются одновременно.

Если статическая память выполнена в виде самостоятельной микросхемы, а не располагается непосредственно на кристалле процессора, линии ее входа зачастую объединяют с линиями выхода, и требуемый режим работы приходится определять по состоянию специального вывода WE (Write Enable). Высокое состояние вывода WE готовит микросхему к чтению данных, а низкое - к записи. Статическая память, размещенную на одном кристалле вместе с процессором, обычно не мультиплексирует, и в этом случае содержимое одной ячейки можно читать параллельно с записью другой (линии входа и выхода ведь раздельные!).

Номера столбцов и строк поступают на декодеры столбца и строки соответственно (см. рис. 10). После декодирования расшифрованный номер строки поступает на дополнительный декодер, вычисляющий, принадлежащую ей матрицу. Оттуда он попадает непосредственно на выборщик строки, который открывает "защелки" требуемой страницы. В зависимости от выбранного режима работы чувствительный усилитель, подсоединенный к битовым линейкам матрицы, либо считывает состояние триггеров соответствующей raw-линейки, либо "перещелкает" их согласно записываемой информации. |